### **Cost Effective 8-Bit Intelligent Analog Flash Microcontrollers**

#### **Description:**

PIC16(L)F1705/9 microcontrollers combine Intelligent Analog integration with low cost and extreme low-power (XLP) to suit a variety of general purpose applications. These 14 and 20-pin devices deliver on-chip Op Amps, Core Independent Peripherals (CLC and COG), Peripheral Pin Select and Zero-Cross Detect, providing for increased design flexibility.

#### **Core Features:**

- C Compiler Optimized RISC Architecture

- Only 49 Instructions

- · Operating Speed:

- 0-32 MHz

- 125 ns minimum instruction cycle

- Interrupt Capability

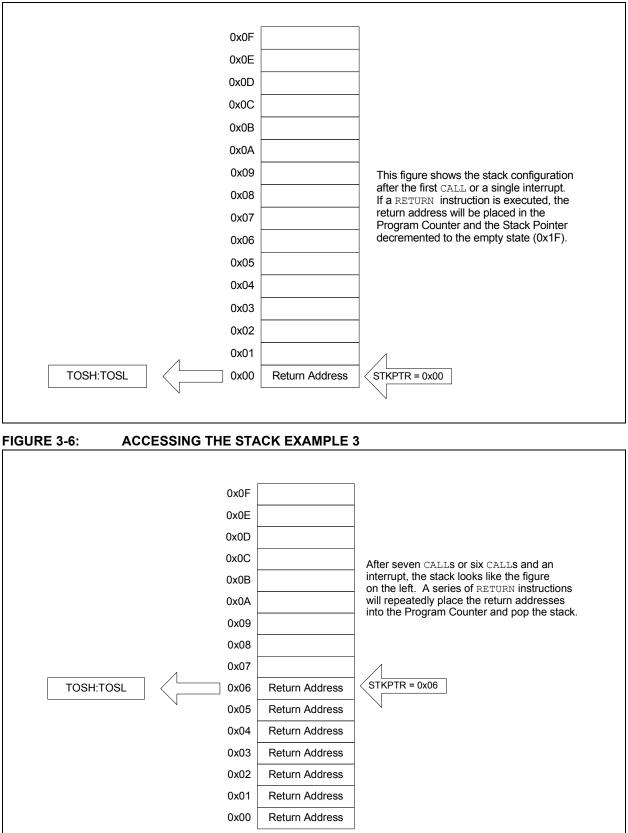

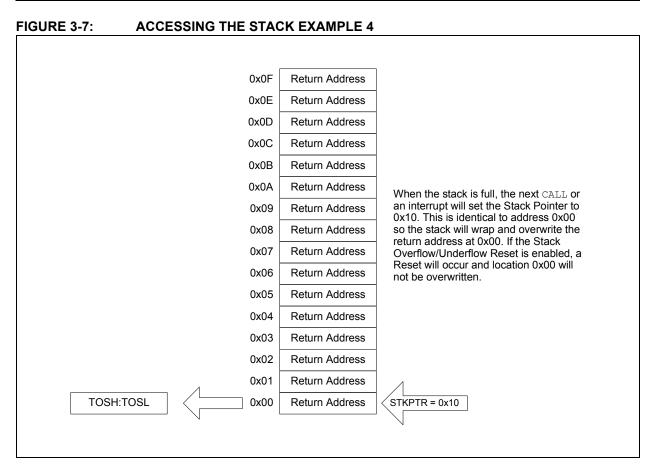

- 16-Level Deep Hardware Stack

- Four 8-bit Timers

- One 16-bit Timer

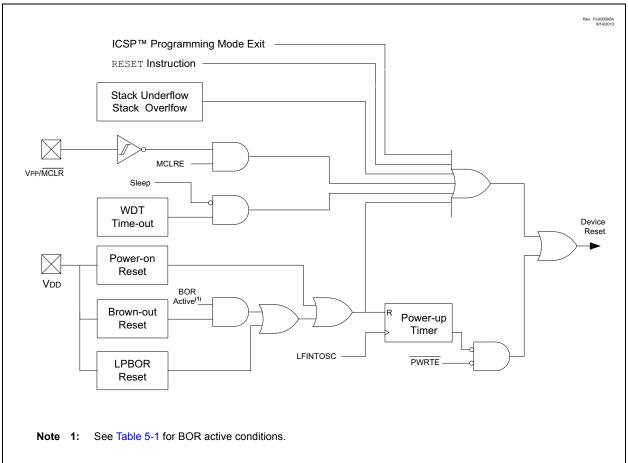

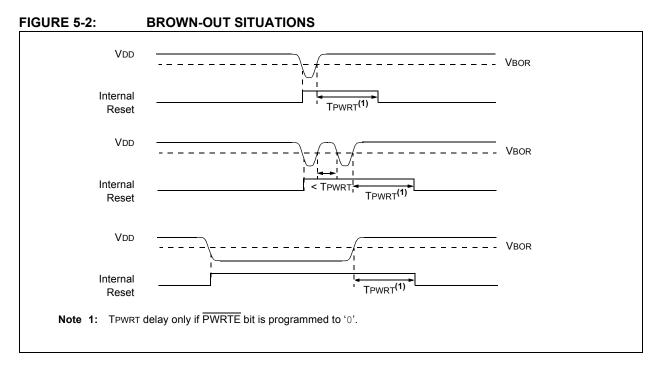

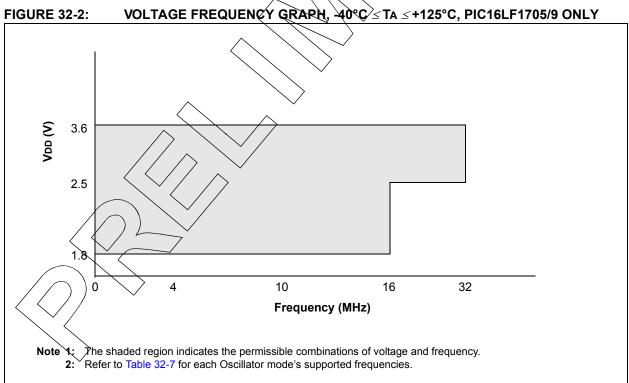

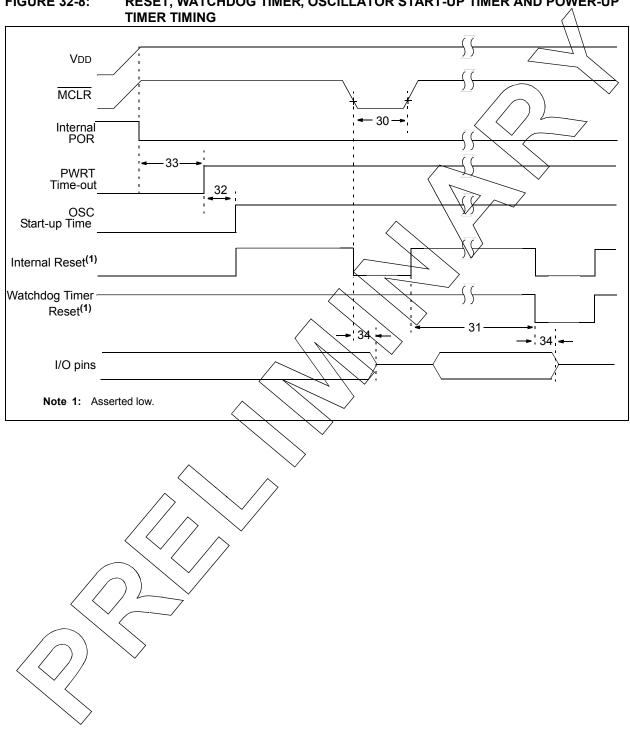

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Low-Power Brown-Out Reset (LPBOR)

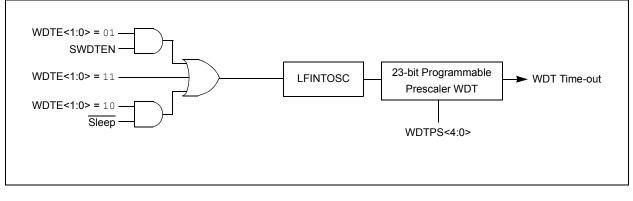

- Programmable Watchdog Timer (WDT) up to 256s

- Programmable Code Protection

#### Memory:

- 8 Kwords Flash Program Memory

- 1024 Bytes Data SRAM Memory

- · Direct, Indirect and Relative Addressing modes

#### **Operating Characteristics:**

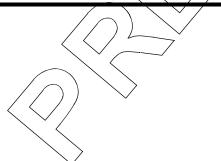

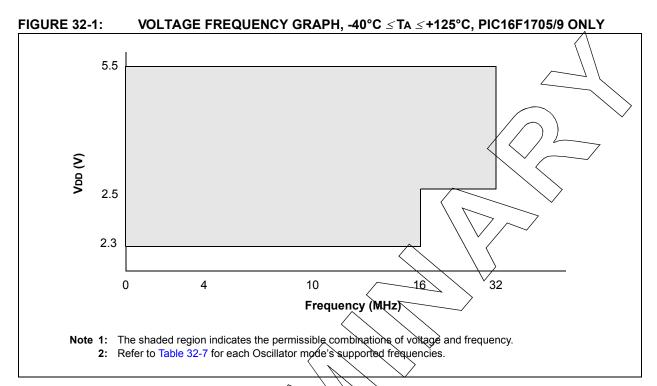

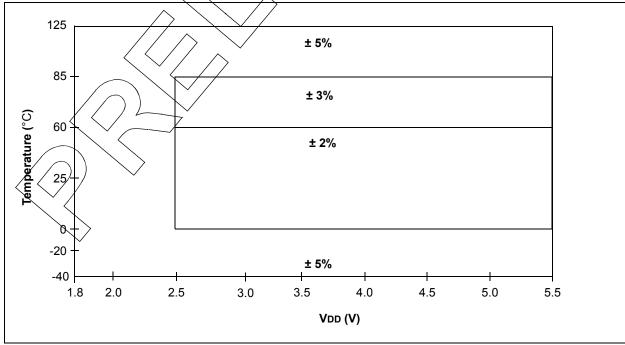

- Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF1705/9)

- 2.3V to 5.5V (PIC16F1705/9)

- Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

#### eXtreme Low-Power (XLP) Features:

- Sleep mode: 50 nA @ 1.8V, typical

- Watchdog Timer: 500 nA @ 1.8V, typical

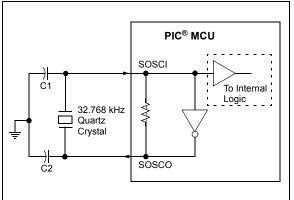

- Secondary Oscillator: 500 nA @ 32 kHz

- Operating Current:

- 8 uA @ 32 kHz, 1.8V, typical

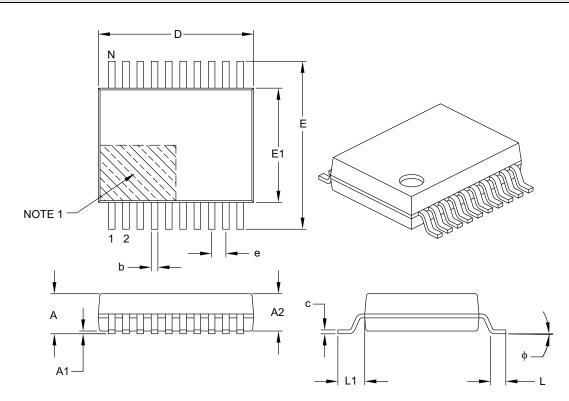

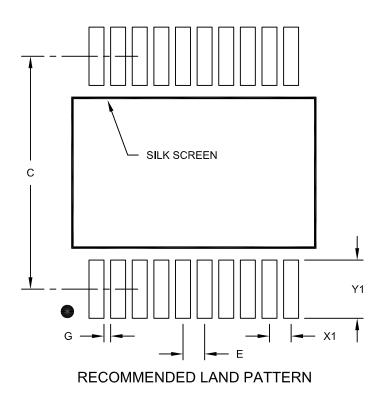

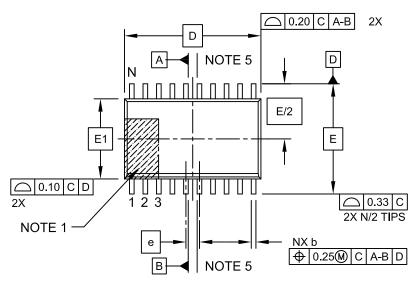

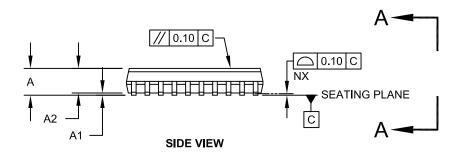

- 32 uA/MHz @ 1.8V, typical

#### **Digital Peripherals:**

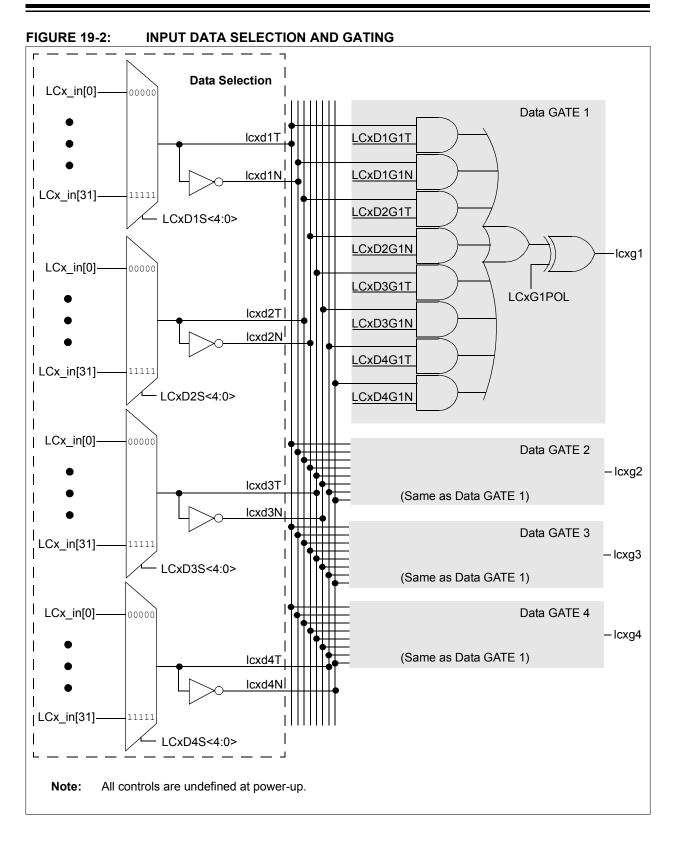

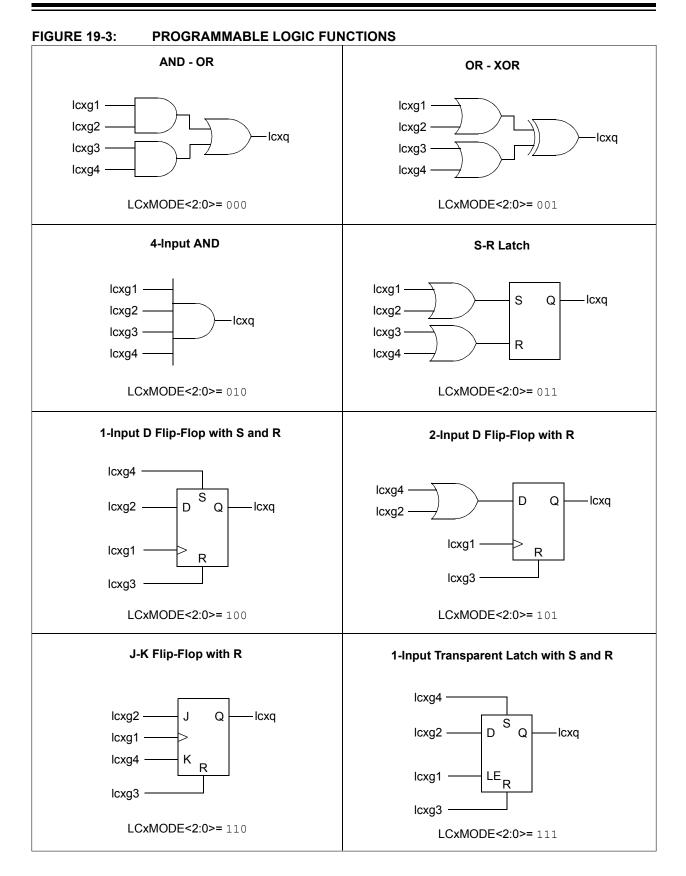

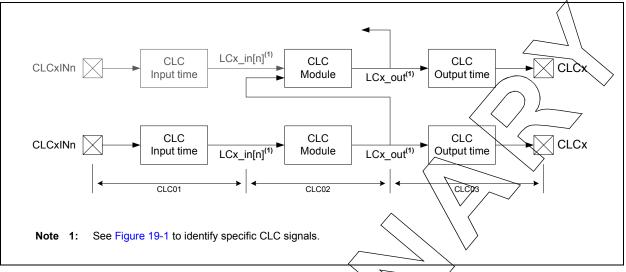

- Configurable Logic Cell (CLC):

- Integrated combinational and sequential logic

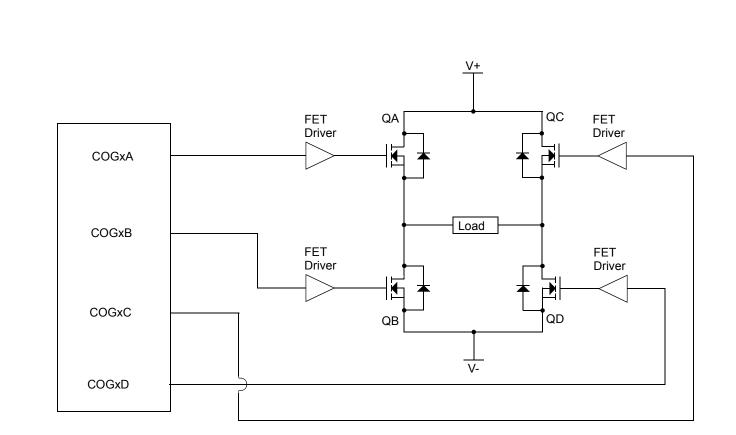

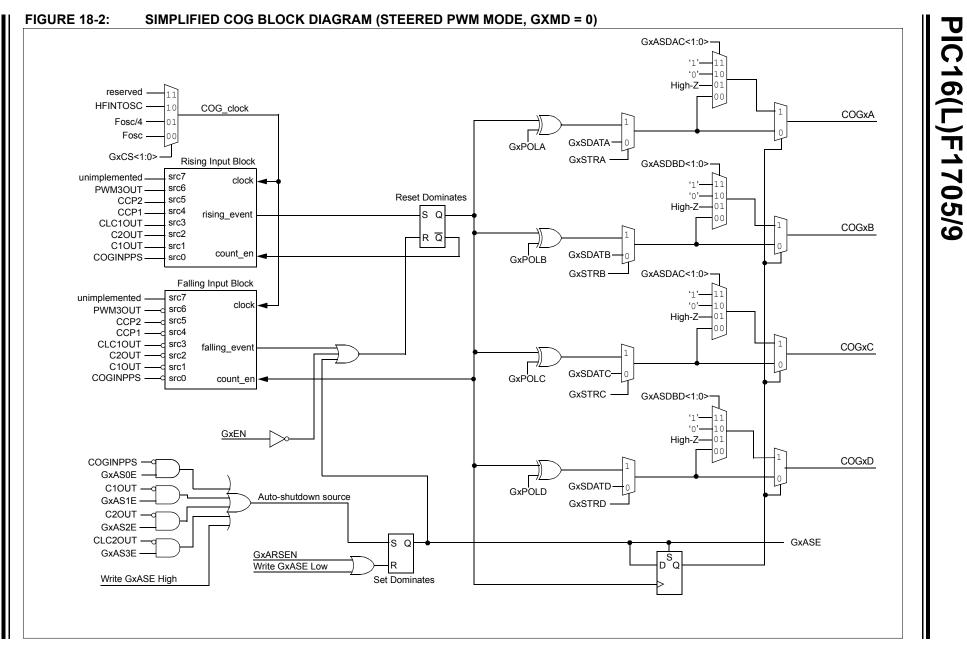

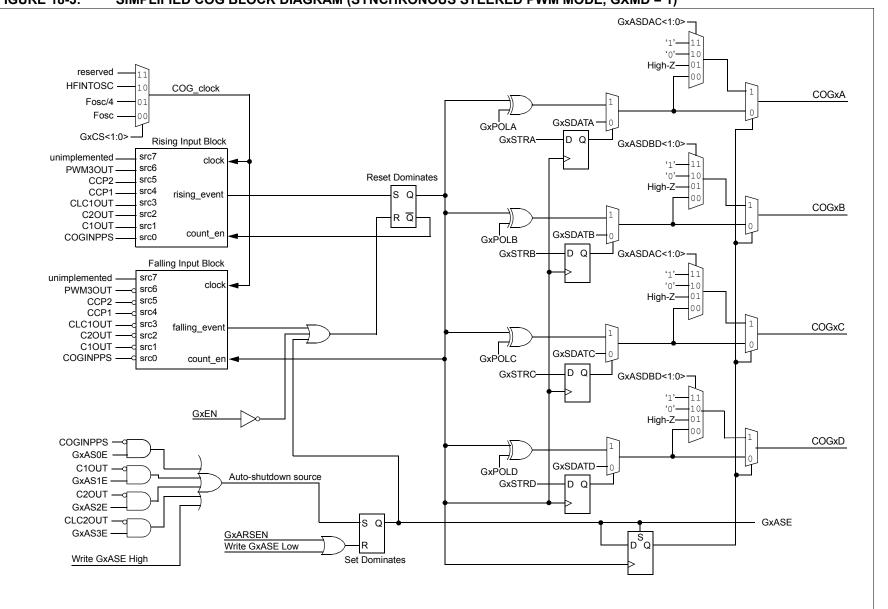

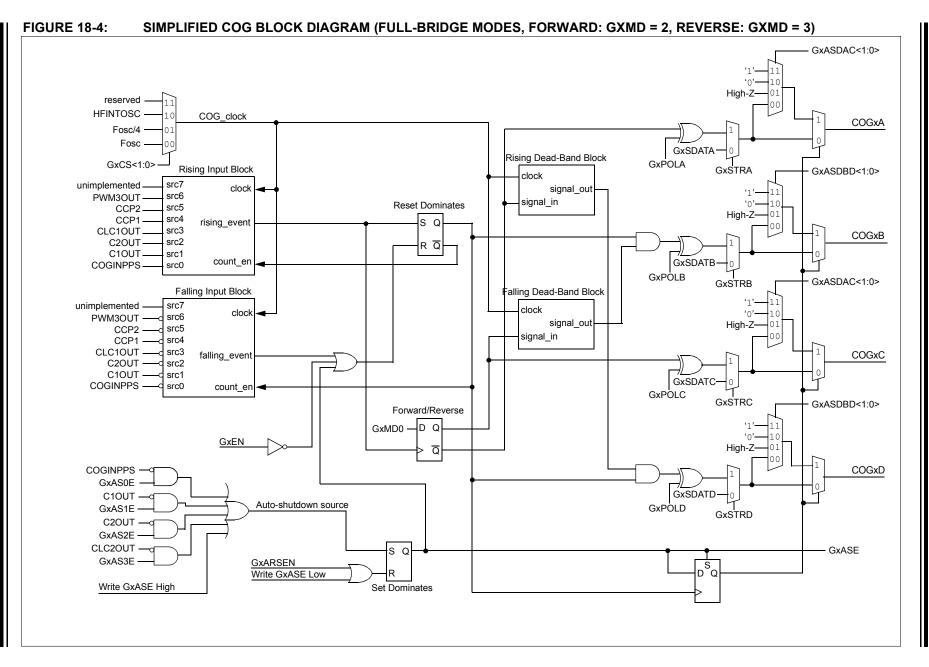

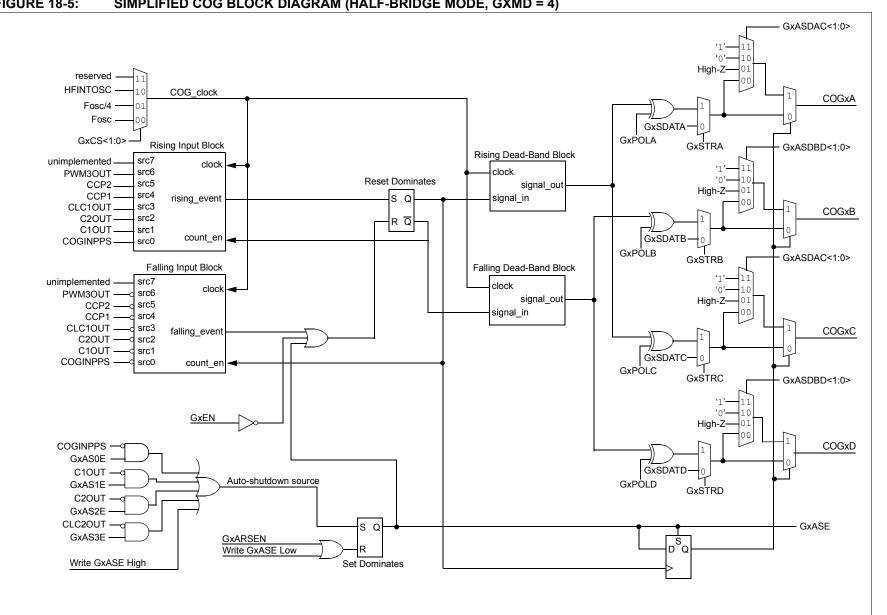

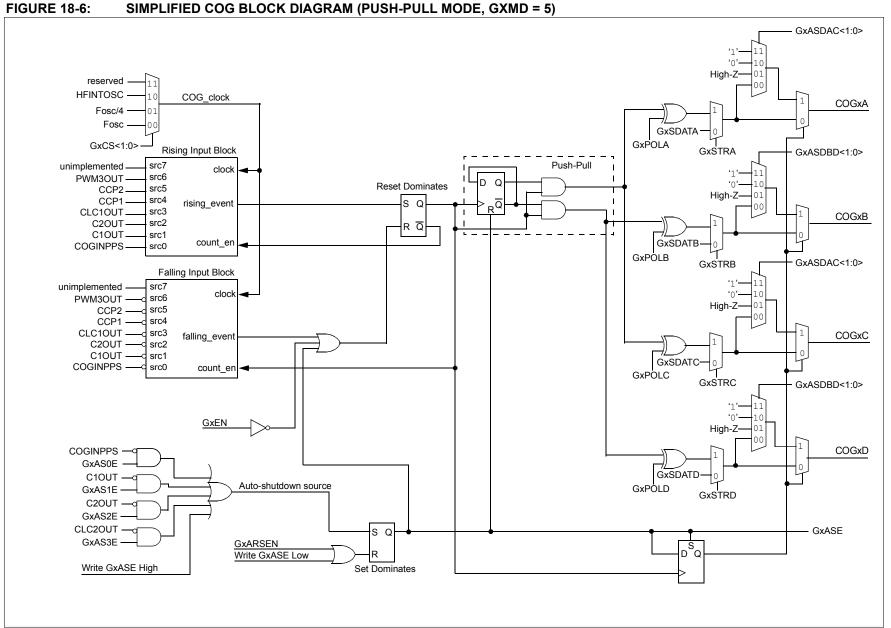

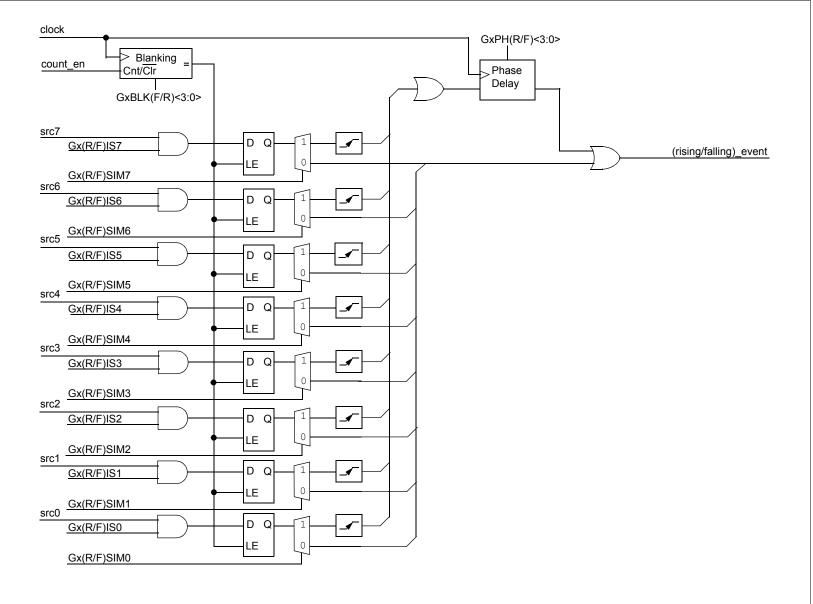

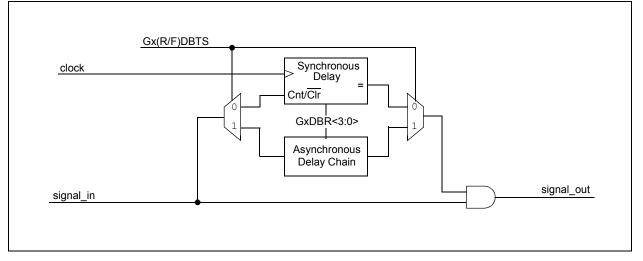

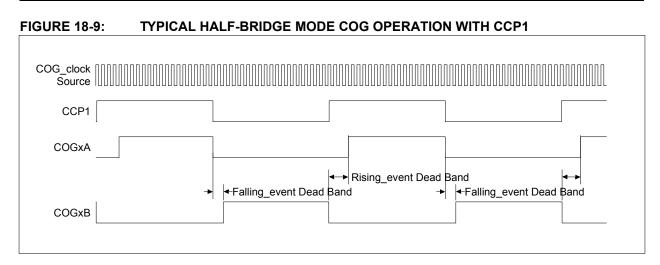

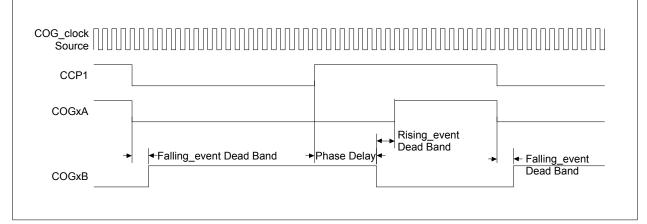

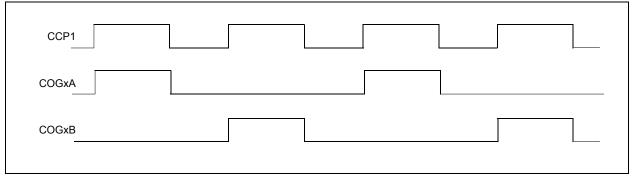

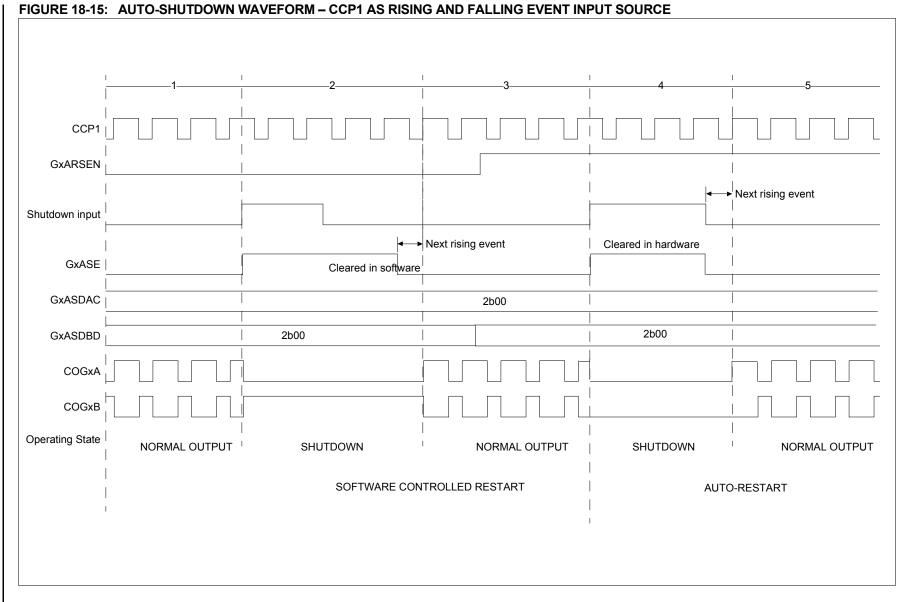

Complementary Output Generator (COG):

- Rising/falling edge dead-band control/ blanking

- Capture/Compare/PWM (CCP) module

- PWM: Two 10-bit Pulse-Width Modulators

- · Serial Communications:

- SPI, I<sup>2</sup>C<sup>™</sup>, RS-232, RS-485, LIN compatible

- Auto-Baud Detect, auto-wake-up on start

- Up to 17 I/O Pins plus One Input-Only Pin:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

#### Intelligent Analog Peripherals:

- · Operational Amplifiers:

- Two configurable rail-to-rail op amps

- Selectable internal and external channels

- 2 MHz gain bandwidth product

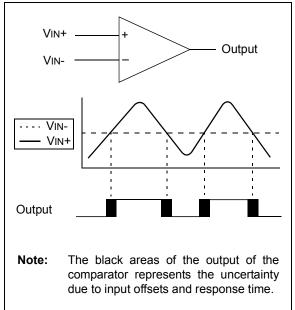

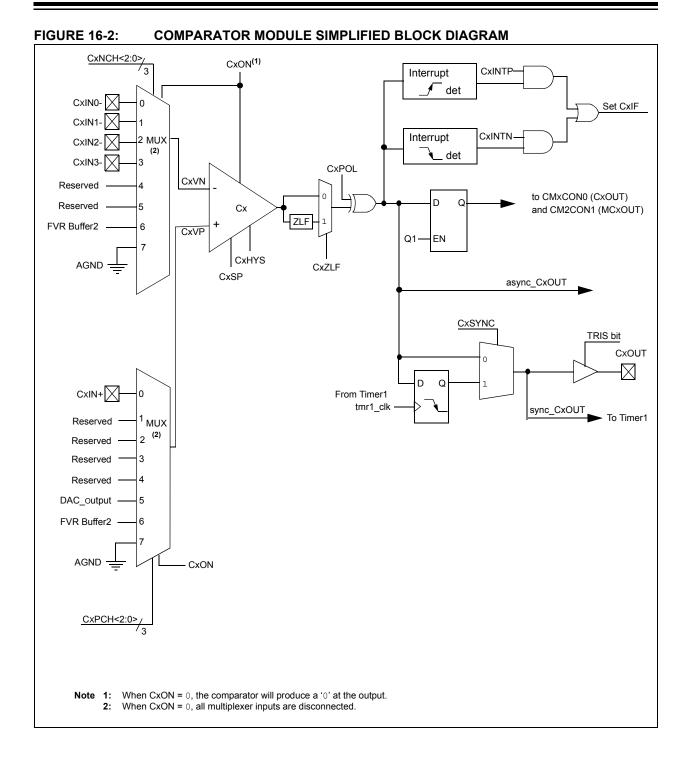

- · High-Speed Comparators:

- Two comparators

- 50 ns response time

- Rail-to-rail inputs

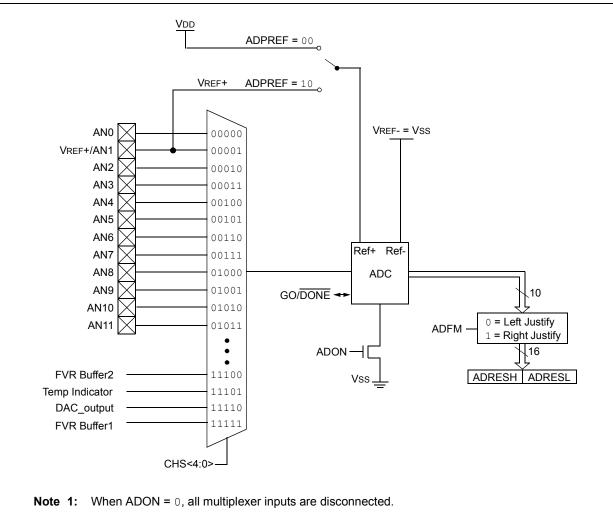

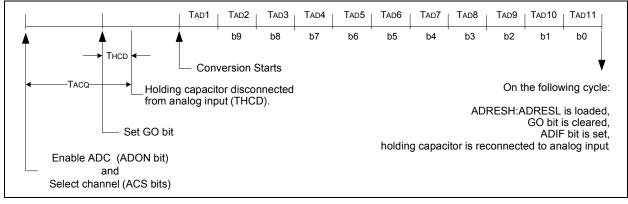

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 12 external channels

- Conversion available during Sleep

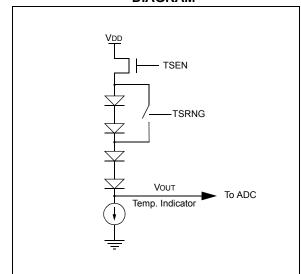

- Temperature indicator

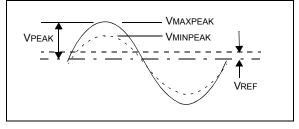

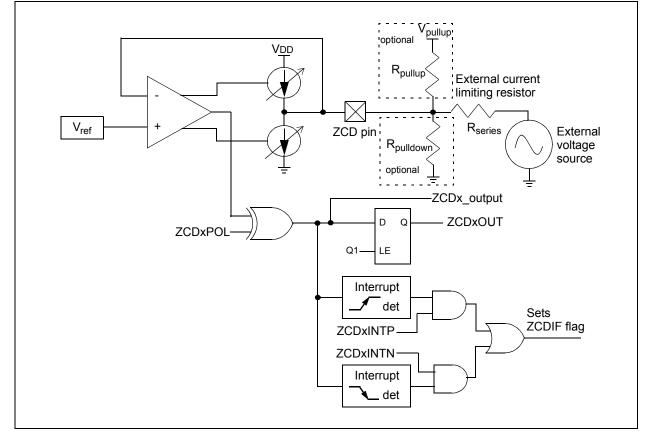

- · Zero-Cross Detector (ZCD):

- Detect when AC signal on pin crosses ground

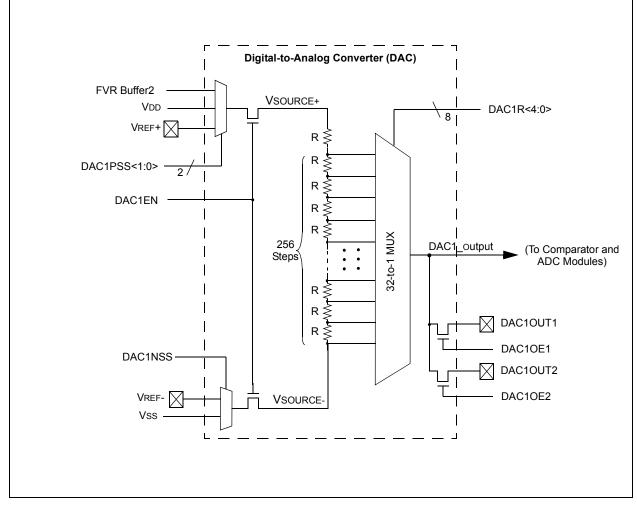

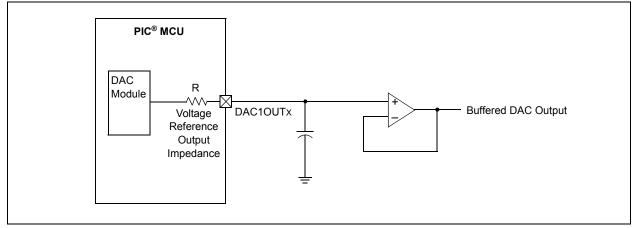

- 8-Bit Digital-to-Analog Converter (DAC):

- Output available externally

- Internal connections to comparators, op amps, Fixed Voltage Reference (FVR) and ADC

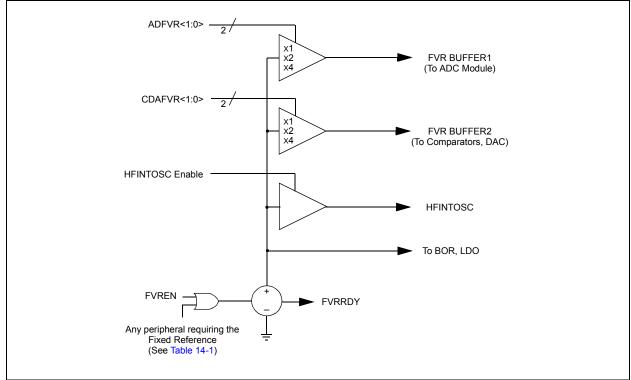

- Internal Voltage Reference module

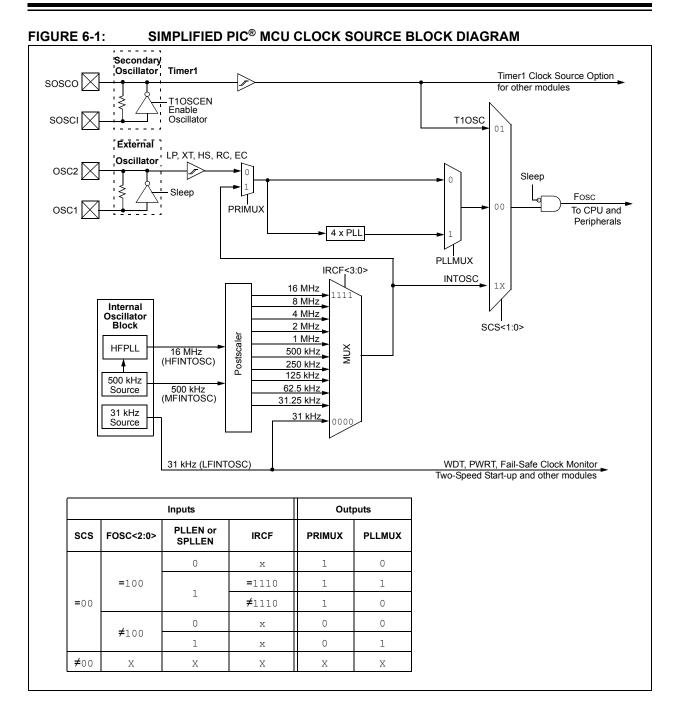

#### **Clocking Structure:**

- 16 MHz Internal Oscillator Block:

- ±1% at calibration

- Selectable frequency range from 0 to 32 MHz

- 31 kHz Low-Power Internal Oscillator

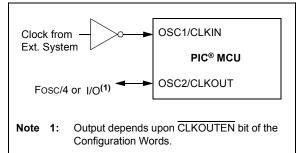

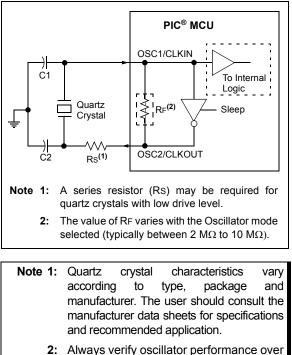

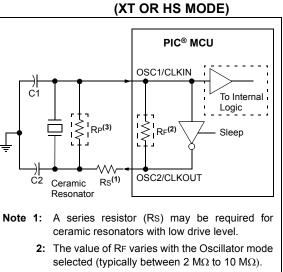

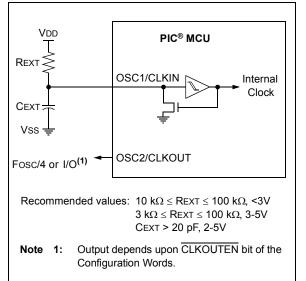

- · External Oscillator Block with:

- Three crystal/resonator modes up to 20 MHz

- Two external clock modes up to 20 MHz

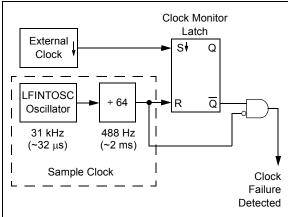

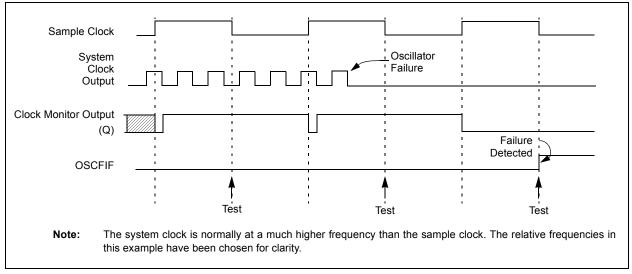

- Fail-Safe Clock Monitor

- Two-Speed Oscillator Start-up

- Oscillator Start-up Timer (OST)

#### PIC16(L)F170x Family Types

#### Programming/Debug Features:

- In-Circuit Debug Integrated On-Chip

- Emulation Header for Advanced Debug:

- Provides trace, background debug and up to 32 hardware break points

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

|               |                  |                                 | Types                | -                    |                 |           |                            |        |            |                      |     |     |     |        |                                            |     |     |                      |     |

|---------------|------------------|---------------------------------|----------------------|----------------------|-----------------|-----------|----------------------------|--------|------------|----------------------|-----|-----|-----|--------|--------------------------------------------|-----|-----|----------------------|-----|

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | I/O's <sup>(2)</sup> | 10-bit ADC (ch) | 8-bit DAC | High-Speed/<br>Comparators | dmA qO | Zero Cross | Timers<br>(8/16-bit) | сср | WMd | 900 | EUSART | MSSP (I <sup>2</sup> C <sup>TM</sup> /SPI) | CLC | Sdd | Debug <sup>(1)</sup> | ΥΓΡ |

| PIC16(L)F1703 | (3)              | 2048                            | 256                  | 12                   | 8               | 0         | 0                          | 2      | 1          | 2/1                  | 2   | 0   | 0   | 0      | 1                                          | 0   | Y   | I/E                  | Y   |

| PIC16(L)F1704 | (1)              | 4096                            | 512                  | 12                   | 8               | 1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                                          | 3   | Y   | I/E                  | Y   |

| PIC16(L)F1705 | (2)              | 8192                            | 1024                 | 12                   | 8               | 1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                                          | 3   | Y   | I/E                  | Y   |

| PIC16(L)F1707 | (3)              | 2048                            | 256                  | 18                   | 12              | 0         | 0                          | 2      | 1          | 2/1                  | 2   | 0   | 0   | 0      | 1                                          | 0   | Υ   | I/E                  | Υ   |

| PIC16(L)F1708 | (1)              | 4096                            | 512                  | 18                   | 12              | 1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                                          | 3   | Υ   | I/E                  | Υ   |

| PIC16(L)F1709 | (2)              | 8192                            | 1024                 | 18                   | 12              | 1         | 2                          | 2      | 1          | 4/1                  | 2   | 2   | 1   | 1      | 1                                          | 3   | Y   | I/E                  | Y   |

Note 1: Debugging Methods: (I) – Integrated on Chip; (H) – using Debug Header; E – using Emulation Header.

2: One pin is input-only.

#### Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS40001715 PIC16(L)F1704/8 Data Sheet, 14/20-Pin Flash, 8-bit Microcontrollers.

- 2: DS40001729A PIC16(L)F1705/9 Data Sheet, 14/20-Pin Flash, 8-bit Microcontrollers.

- 3: DS40001722 PIC16(L)F1703/7 Data Sheet, 14/20-Pin Flash, 8-bit Microcontrollers.

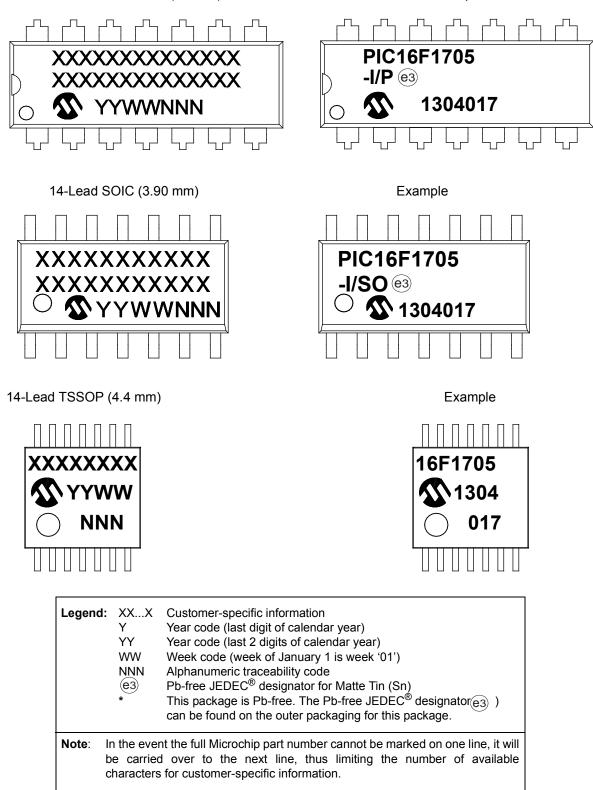

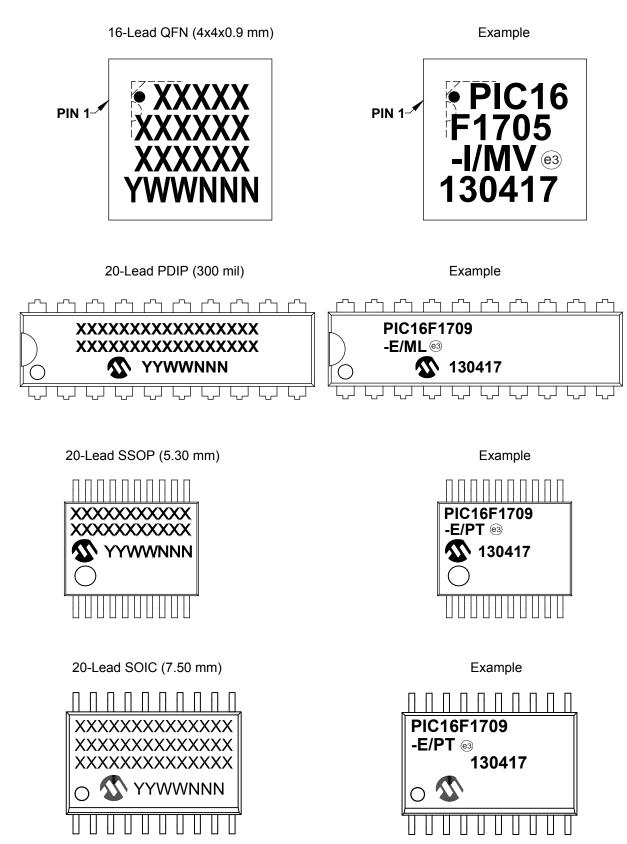

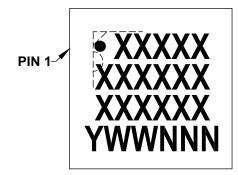

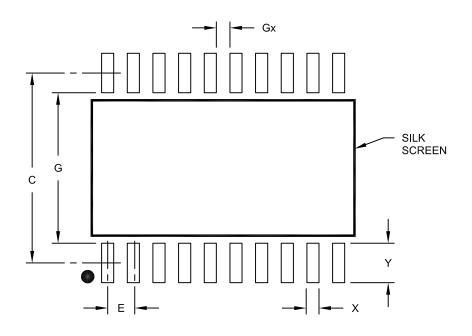

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

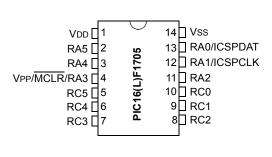

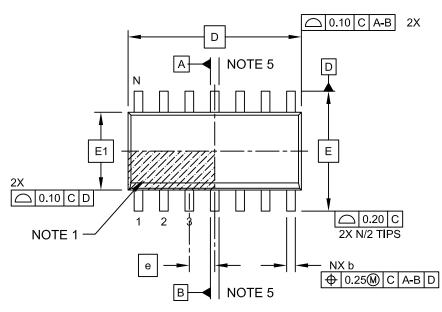

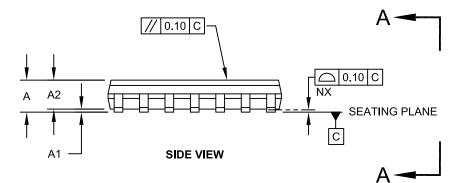

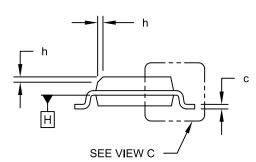

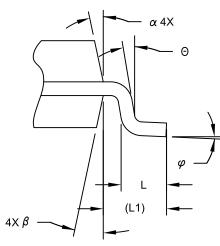

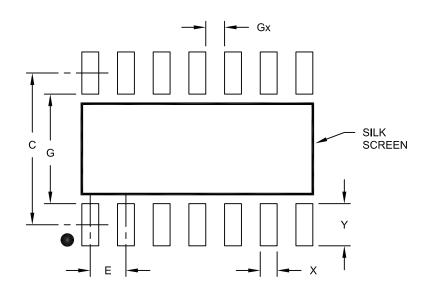

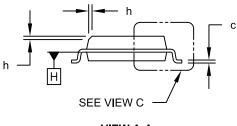

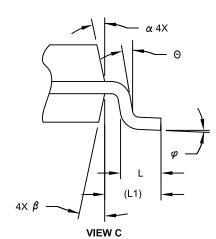

#### FIGURE 1: 14-PIN DIAGRAM FOR PIC16(L)F1705

#### PDIP, SOIC, TSSOP

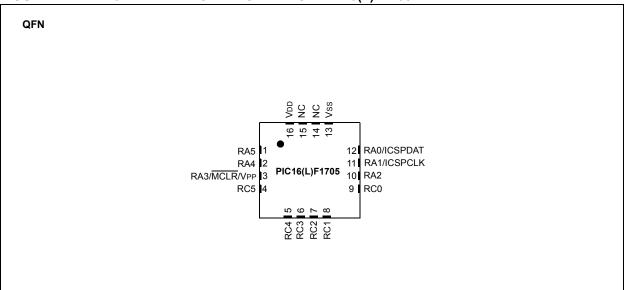

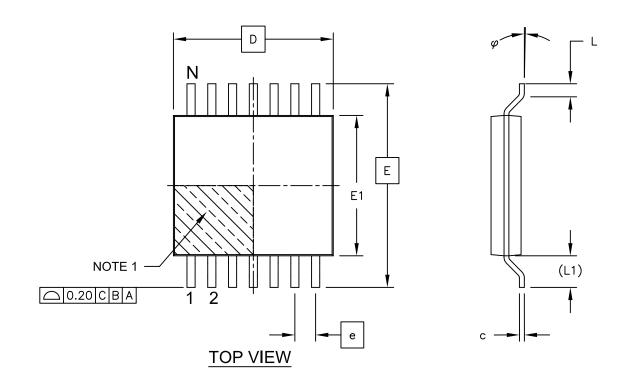

#### FIGURE 2: 16-PIN PACKAGE DIAGRAM FOR PIC16(L)F1705

#### TABLE 1: 14/16-PIN ALLOCATION TABLE (PIC16(L)F1705)

|                    | ••             | • • • • | ••••••• |           |                  |         |          |            |                               |                     |         |                      |                                          |                     |                       |                           |         |                |

|--------------------|----------------|---------|---------|-----------|------------------|---------|----------|------------|-------------------------------|---------------------|---------|----------------------|------------------------------------------|---------------------|-----------------------|---------------------------|---------|----------------|

| 1/O <sup>(2)</sup> | PDIP/SOIC/SSOP | QFN     | ADC     | Reference | Comparator       | Op Amp  | DAC      | Zero Cross | Timers                        | ССР                 | MWG     | 900                  | dssm                                     | EUSART              | CLC                   | Interrupt                 | Pull-up | Basic          |

| RA0                | 13             | 12      | AN0     | VREF-     | C1IN+            | —       | DAC1OUT  | —          | —                             | —                   |         | -                    | -                                        | —                   | -                     | IOC                       | Y       | ICSPDAT        |

| RA1                | 12             | 11      | AN1     | VREF+     | C1IN0-<br>C2IN0- | -       | _        | -          | —                             | —                   |         | -                    | -                                        | -                   | —                     | IOC                       | Y       | ICSPCLK        |

| RA2                | 11             | 10      | AN2     |           | _                | —       | DAC1OUT2 | ZCD        | T0CKI <sup>(1)</sup>          | —                   |         | COGIN <sup>(1)</sup> | _                                        | -                   | —                     | INT <sup>(1)</sup><br>IOC | Y       | _              |

| RA3                | 4              | 3       | —       | —         | -                | —       | —        | _          | —                             | —                   |         | —                    |                                          | _                   | _                     | IOC                       | Y       | MCLR<br>VPP    |

| RA4                | 3              | 2       | AN3     | _         |                  | _       | —        | —          | T1G <sup>(1)</sup><br>SOSCO   | _                   |         | _                    |                                          |                     |                       | IOC                       | Y       | CLKOUT<br>OSC2 |

| RA5                | 2              | 1       | _       | -         | -                | —       | _        | —          | T1CKI <sup>(1)</sup><br>SOSCI | —                   |         | _                    | -                                        |                     | CLCIN3 <sup>(1)</sup> | IOC                       | Y       | CLKIN<br>OSC1  |

| RC0                | 10             | 9       | AN4     |           | C2IN+            | OPA1IN+ | —        | -          | -                             | —                   |         | -                    | SCK <sup>(1)</sup><br>SCL <sup>(3)</sup> | -                   | —                     | IOC                       | Y       | _              |

| RC1                | 9              | 8       | AN5     | —         | C1IN1-<br>C2IN1- | OPA1IN- | —        | _          | —                             | —                   |         | —                    | SDI <sup>(1)</sup><br>SDA <sup>(3)</sup> | _                   | CLCIN2 <sup>(1)</sup> | IOC                       | Y       | _              |

| RC2                | 8              | 7       | AN6     | -         | C1IN2-<br>C2IN2- | OPA10UT | —        | —          | —                             | _                   |         | _                    |                                          | _                   | _                     | IOC                       | Y       | _              |

| RC3                | 7              | 6       | AN7     | —         | C1IN3-<br>C2IN3- | OPA2OUT | —        | —          | —                             | CCP2 <sup>(1)</sup> |         | —                    | <u>SS</u> (1)                            |                     | CLCIN0 <sup>(1)</sup> | IOC                       | Y       | _              |

| RC4                | 6              | 5       | _       | —         | -                | OPA2IN- | _        | _          | -                             | _                   |         | -                    | -                                        | CK <sup>(1)</sup>   | CLCIN1 <sup>(1)</sup> | IOC                       | Y       | —              |

| RC5                | 5              | 4       | _       | —         |                  | OPA2IN+ | —        | _          | —                             | CCP1 <sup>(1)</sup> |         | —                    | -                                        | RX <sup>(1,3)</sup> | _                     | IOC                       | Y       | —              |

| Vdd                | 1              | 16      | _       | _         |                  | _       | _        | _          | _                             | _                   |         | _                    |                                          | _                   |                       |                           |         | Vdd            |

| Vss                | 14             | 13      | —       | —         | -                | —       | —        | —          | _                             | —                   |         | _                    | _                                        | —                   | -                     | —                         | —       | Vss            |

|                    | _              | —       | _       | _         | C10UT            | _       | _        | _          | _                             | CPP1                | PWM3OUT | COGA                 | SDA <sup>(3)</sup>                       | СК                  | CLC1OUT               |                           |         | _              |

| OUT <sup>(2)</sup> | —              | —       | -       | —         | C2OUT            | —       | —        | —          | —                             | CPP2                | PWM4OUT | COGB                 | SCL <sup>(3)</sup>                       | DT <sup>(3)</sup>   | CLC2OUT               | —                         | —       | —              |

|                    | —              | _       | _       | —         | _                | —       | —        | _          | —                             | —                   | —       | COGC                 | SDO                                      | TX                  | CLC3OUT               | —                         | —       | —              |

|                    | —              | —       | _       | —         | _                | —       | —        | _          | —                             | —                   | _       | COGD                 | SCK                                      | —                   |                       | _                         |         |                |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-3.

#### TABLE 2: 20-PIN ALLOCATION TABLE (PIC16(L)F1709)

| IADEE              |                    | 201 |      |           |                  |         |          | 00)        |                             |                     |         |                      |                                          |                     |                       |                           |         |                |

|--------------------|--------------------|-----|------|-----------|------------------|---------|----------|------------|-----------------------------|---------------------|---------|----------------------|------------------------------------------|---------------------|-----------------------|---------------------------|---------|----------------|

| I/O <sup>(2)</sup> | PDIP/SOIC/<br>SSOP | QFN | ADC  | Reference | Comparator       | Op Amp  | DAC      | Zero Cross | Timers                      | ссь                 | MWd     | 900                  | MSSP                                     | EUSART              | CLC                   | Interrupt                 | Pull-up | Basic          |

| RA0                | 19                 | 16  | AN0  | VREF-     | C1IN+            | _       | DAC1OUT  | _          | —                           | -                   | —       | _                    |                                          | —                   | —                     | IOC                       | Y       | ICSPDAT        |

| RA1                | 18                 | 15  | AN1  | VREF+     | C1IN0-<br>C2IN0- | _       | —        | -          | —                           | -                   | —       | _                    | —                                        | —                   | _                     | IOC                       | Y       | ICSPCLK        |

| RA2                | 17                 | 14  | AN2  | —         | —                | —       | DAC1OUT2 | ZCD        | T0CKI <sup>(1)</sup>        | —                   | —       | COGIN <sup>(1)</sup> | —                                        | —                   | —                     | INT <sup>(1)</sup><br>IOC | Y       | —              |

| RA3                | 4                  | 1   | —    | _         | —                | _       | —        | -          | —                           | -                   | —       | _                    | —                                        | —                   | _                     | IOC                       | Y       | MCLR<br>VPP    |

| RA4                | 3                  | 20  | AN3  | _         | —                | —       | —        | _          | T1G <sup>(1)</sup><br>SOSCO | -                   | —       | —                    | —                                        | _                   | —                     | IOC                       | Y       | CLKOUT<br>OSC2 |

| RA5                | 2                  | 19  | —    | —         | —                | —       | _        |            | T1CKI<br>SOSCI              | _                   | _       | —                    | —                                        | _                   | CLCIN3 <sup>(1)</sup> | IOC                       | Y       | CLKIN<br>OSC1  |

| RB4                | 13                 | 10  | AN10 | —         | —                | OPA1IN- | —        |            | -                           |                     | —       | _                    | SCK <sup>(1)</sup><br>SDA <sup>(3)</sup> | -                   | _                     | IOC                       | Y       | _              |

| RB5                | 12                 | 9   | AN11 | _         | _                | OPA1IN+ | —        | _          | -                           | _                   | —       | _                    | _                                        | RX <sup>(1,3)</sup> |                       | IOC                       | Y       | _              |

| RB6                | 11                 | 8   | —    | —         | —                | _       | —        | _          | —                           | _                   | —       | —                    | SDI <sup>(1)</sup><br>SCL <sup>(3)</sup> | _                   | —                     | IOC                       | Y       | —              |

| RB7                | 10                 | 7   | _    | —         | _                | _       | _        | -          | _                           |                     |         | —                    | —                                        | CK <sup>(1)</sup>   | _                     | IOC                       | Y       | _              |

| RC0                | 16                 | 13  | AN4  | _         | C2IN+            | _       | _        |            | _                           |                     | _       | _                    | _                                        | _                   | _                     | IOC                       | Y       | _              |

| RC1                | 15                 | 12  | AN5  | —         | C1IN1-<br>C2IN1- | —       |          | _          | —                           | _                   |         | —                    | —                                        | —                   | CLCIN2 <sup>(1)</sup> | IOC                       | Y       | —              |

| RC2                | 14                 | 11  | AN6  | _         | C1IN2-<br>C2IN2- | OPA10UT | —        | _          | —                           | _                   | —       | —                    | —                                        | —                   | —                     | IOC                       | Y       | —              |

| RC3                | 7                  | 4   | AN7  | —         | C1IN3-<br>C2IN3- | OPA2OUT | —        | _          | —                           | CCP2 <sup>(1)</sup> | —       | —                    | —                                        | —                   | CLCIN0 <sup>(1)</sup> | IOC                       | Y       | _              |

| RC4                | 6                  | 3   |      | _         | _                | _       | _        | _          | _                           | _                   | _       | _                    | _                                        |                     | CLCIN1 <sup>(1)</sup> | IOC                       | Y       | —              |

| RC5                | 5                  | 2   | _    | _         | _                | _       | _        |            | _                           | CCP1 <sup>(1)</sup> | _       | _                    | _                                        | _                   | _                     | IOC                       | Y       | _              |

| RC6                | 8                  | 5   | AN8  | _         | _                | OPA2IN- | _        | _          | _                           | _                   | _       | _                    | SS <sup>(1)</sup>                        | -                   | _                     | IOC                       | Y       | —              |

| RC7                | 9                  | 6   | AN9  | _         | —                | OPA2IN+ | _        |            | —                           |                     | _       | —                    | —                                        | _                   | _                     | IOC                       | Y       | —              |

| VDD                | 1                  | 18  |      | _         | _                | _       | _        | _          | _                           | _                   | _       | _                    | _                                        | -                   | _                     | _                         | —       | VDD            |

| Vss                | 20                 | 17  | _    | _         | _                | _       | _        |            | _                           |                     | _       | _                    | _                                        | _                   | _                     |                           | _       | Vss            |

|                    | _                  | _   | _    | _         | C1OUT            | —       | _        |            | _                           | CPP1                | PWM3OUT | COGA                 | SDA <sup>(3)</sup>                       | СК                  | CLC10UT               | _                         | _       | _              |

| OUT <sup>(2)</sup> | —                  | _   | _    | _         | C2OUT            | —       | _        |            | —                           | CPP2                | PWM4OUT | COGB                 | SCL <sup>(3)</sup>                       | DT <sup>(3)</sup>   | CLC2OUT               | _                         | —       | —              |

| 001-               | _                  | _   | _    | _         | _                | —       | _        | _          | _                           | _                   | _       | COGC                 | SDO                                      | ΤX                  | CLC3OUT               | _                         | —       | _              |

|                    | —                  |     | _    | —         | _                | —       | _        |            | _                           |                     | —       | COGD                 | SCK                                      | _                   | _                     | _                         | _       | _              |

|                    |                    |     |      |           |                  |         |          |            |                             |                     |         |                      |                                          |                     |                       |                           |         |                |

PIC16(L)F1705/9

© 2013 Microchip Technology Inc.

Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-2. Note 1:

All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-3. 2:

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

DS40001729A-page 6

Preliminary

#### **Table of Contents**

| 1.0 Device Overview                                                            | 0   |

|--------------------------------------------------------------------------------|-----|

| 2.0 Enhanced Mid-Range CPU                                                     |     |

| 3.0 Memory Organization                                                        |     |

| 4.0 Device Configuration                                                       |     |

| 5.0 Resets                                                                     |     |

| 6.0 Oscillator Module (with Fail-Safe Clock Monitor)                           |     |

| 7.0 PIC16(L)F1705/9 Interrupts                                                 |     |

| 8.0 Power-Down Mode (Sleep)                                                    |     |

| 9.0 Watchdog Timer (WDT)                                                       |     |

| 10.0 Flash Program Memory Control                                              |     |

| 11.0 I/O Ports                                                                 |     |

| 12.0 Peripheral Pin Select (PPS) Module                                        |     |

| 13.0 nterrupt-On-Change                                                        |     |

| 14.0 Fixed Voltage Reference (FVR)                                             |     |

| 15.0 Temperature Indicator Module                                              |     |

| 16.0 Comparator Module                                                         |     |

| 17.0 Pulse-Width Modulation (PWM)                                              |     |

| 18.0 Complementary Output Generator (COG) Module                               |     |

| 19.0 Configurable Logic Cell (CLC)                                             |     |

| 20.0 Analog-to-Digital Converter (ADC) Module                                  |     |

| 21.0 Operational Amplifier (OPA) Modules                                       |     |

| 22.0 8-Bit Digital-to-Analog Converter (DAC1) Module                           |     |

| 23.0 Zero-Cross Detection (ZCD) Module                                         |     |

| 24.0 Timer0 Module                                                             |     |

| 25.0 Timer1 Module with Gate Control                                           | 247 |

| 26.0 Timer2/4/6 Module                                                         |     |

| 27.0 Capture/Compare/PWM Modules                                               | 263 |

| 28.0 Master Synchronous Serial Port (MSSP) Module                              | 271 |

| 29.0 Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 324 |

| 30.0 In-Circuit Serial Programming™ (ICSP™)                                    | 355 |

| 31.0 Instruction Set Summary                                                   | 357 |

| 32.0 Electrical Specifications                                                 | 371 |

| 33.0 DC and AC Characteristics Graphs and Charts                               | 404 |

| 34.0 Development Support                                                       | 418 |

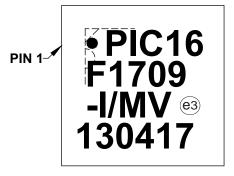

| 35.0 Packaging Information                                                     | 422 |

| Appendix A: Data Sheet Revision History                                        | 441 |

| The Microchip Web Site                                                         | 448 |

| Customer Change Notification Service                                           |     |

| Customer Support                                                               |     |

| Product Identification System                                                  | 449 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 1.0 DEVICE OVERVIEW

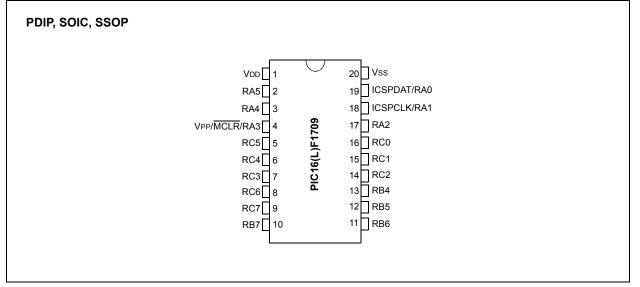

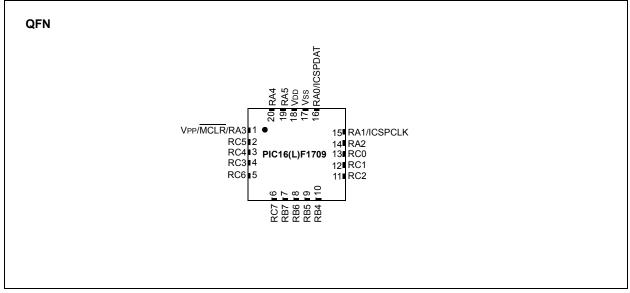

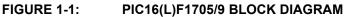

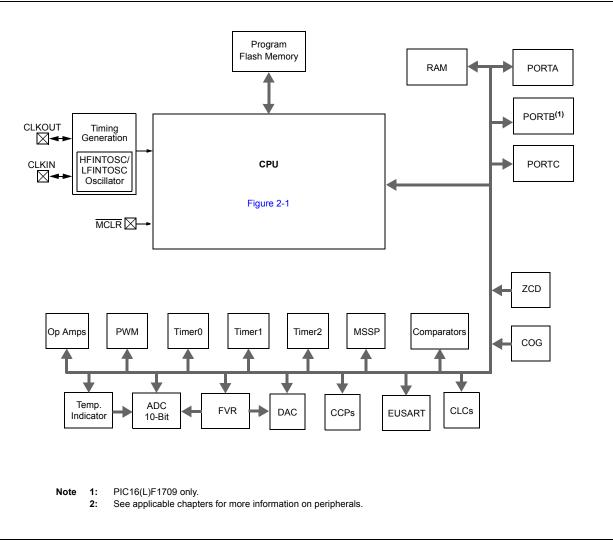

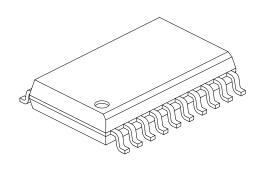

The PIC16(L)F1705/9 are described within this data sheet. They are available in 14-pin and 20-pin DIP packages and 16-pin and 20-pin QFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F1705/9 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral90<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50 |                              |             |               |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|---------------|---------------|

| Digital-to-Analog Converter (DAC)         •         •           Complementary Output Generator (COG)         •         •           Fixed Voltage Reference (FVR)         •         •           Zero-Cross Detection (ZCD)         •         •           Temperature Indicator         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           Comparators         C1         •           Configurable Logic Cell (CLC)         •         •           Configurable Logic Cell (CLC)         •         •           CLC1         •         •           CLC2         •         •           CLC2         •         •           CLC2         •         •           CLC2         •         •           CLC3         •         •           Enhanced Universal Synchronous/Asynchronous         •         •           Receiver/Transmitter (EUSART)         •         •           Master Synchronous Serial Ports         •         •           Op Amp         •         •         •           Pulse-Width Modulator (PWM)         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |             | PIC16(L)F1705 | PIC16(L)F1709 |

| Complementary Output Generator (COG)       •         Fixed Voltage Reference (FVR)       •         Zero-Cross Detection (ZCD)       •         Temperature Indicator       •         Capture/Compare/PWM (CCP/ECCP) Modules         CCP1       •         CCP2       •         Comparators       •         Configurable Logic Cell (CLC)       •         Clc2       •         Configurable Logic Cell (CLC)       •         Clc2       •         Configurable Logic Cell (CLC)       •         Clc2       •         Clc2       •         Clc2       •         Configurable Logic Cell (CLC)       •         Clc2       •         Clc2       •         Clc3       •         Enhanced Universal Synchronous/Asynchronous         Receiver/Transmitter (EUSART)       •         Master Synchronous Serial Ports         Op Amp       •         Op Amp 1       •         Op Amp 2       •         Pulse-Width Modulator (PWM)       •         PWM3       •         Timer0       •         Timer1       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Analog-to-Digital Converter  | (ADC)       | ٠             | •             |

| Fixed Voltage Reference (FVR)       •         Zero-Cross Detection (ZCD)       •         Temperature Indicator       •         Capture/Compare/PWM (CCP/ECCP) Modules         CCP1       •         CCP2       •         Comparators       •         C1       •         C1       •         C0       •         C2       •         Configurable Logic Cell (CLC)       •         CLC1       •         CLC2       •         CLC3       •         Enhanced Universal Synchronous/Asynchronous         Receiver/Transmitter (EUSART)       •         Master Synchronous Serial Ports       •         Op Amp       •         Op Amp 1       •         Op Amp 2       •         Pulse-Width Modulator (PWM)       •         Timers       •         Timer0       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital-to-Analog Converter  | (DAC)       | ٠             | •             |

| Zero-Cross Detection (ZCD)         •         •           Temperature Indicator         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           Comparators         •         •           Comparators         •         •           Configurable Logic Cell (CLC)         •         •           CLC1         •         •           CLC2         •         •           CLC3         •         •           Master Synchronous Serial Ports         •         •           Op Amp 1         •         •         •           Op Amp 2         •         •         •           Pulse-Width Modulator (PWM)         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Complementary Output Gene    | rator (COG) | ٠             | •             |

| Temperature Indicator         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         CCP1         •           CCP2         •         •           Comparators         CCP2         •           Comparators         C1         •           Configurable Logic Cell (CLC)         •         •           Clc2         •         •           Clc3         •         •           Clc3         •         •           Clc3         •         •           Master Synchronous Serial Ports         •         •           Op Amp         •         •           Pulse-Width Modulator (PWM)         •         •           PWM4         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fixed Voltage Reference (F)  | /R)         | ٠             | •             |

| Capture/Compare/PWM (CCP/ECCP) Modules           CCP1         •           CCP2         •           Comparators         •           Comparators         •           Configurable Logic Cell (CLC)         •           CLC1         •           CLC2         •           CLC2         •           CLC2         •           CLC3         •           Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)         •           Master Synchronous Serial Ports         •           Op Amp         •           Op Amp         •           Pulse-Width Modulator (PWM)         •           PWM3         •           PWM4         •           Timers         Timer0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Zero-Cross Detection (ZCD)   |             | •             | •             |

| CCP1 •CCP2 •ComparatorsC1 •C2 •Configurable Logic Cell (CLC)CLC1 •CLC2 •CLC2 •CLC3 •CLC3 •CLC3 •CLC3 •Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)EUSART •Master Synchronous Serial PortsOp AmpOp AmpOp Amp 1 •Op Amp 2 •Pulse-Width Modulator (PWM)PWM3 •TimersTimer0 •Timer0 •Timer1 •Timer1 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Temperature Indicator        |             | ٠             | ٠             |

| CCP2•ComparatorsC1•C2•Configurable Logic Cell (CLC)CLC1•CLC2•CLC3•CLC3•CLC3•Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)EUSART•Master Synchronous Serial PortsOp Amp•Op Amp1•Op Amp2•Pulse-Width Modulator (PWM)PWM3•TimersTimer0Timer1•Timer1•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Capture/Compare/PWM (CC      | P/ECCP) Mod | ules          |               |

| Comparators         C1         C2         C2         Configurable Logic Cell (CLC)         CLC1         CLC2         CLC3         Enhanced Universal Synchronous/Asynchronous         Receiver/Transmitter (EUSART)         Master Synchronous Serial Ports         Master Synchronous Serial Ports         Op Amp         Op Amp 1         Op Amp 2         Pulse-Width Modulator (PWM)         PWM3         PWM4         Timers         Timer0         Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              | CCP1        | ٠             | •             |

| C1C2Configurable Logic Cell (CLC)CLC1CLC2CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3CLC3EUSARTMaster Synchronous Serial PortsMaster Synchronous Serial PortsOp AmpOp Amp 1Op Amp 2Pulse-Width Modulator (PWM)PWM3PWM4TimersTimer0Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              | CCP2        | •             | •             |

| C2•Configurable Logic Cell (CLC)CLC1•CLC2•CLC3•CLC3•CLC3•Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)EUSART•Master Synchronous Serial PortsMaster Synchronous Serial PortsOp Amp•Op Amp•Op Amp 1•Op Amp 2•Pulse-Width Modulator (PWM)PWM3•Timers•Timer0•Timer1•Timer1•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Comparators                  |             |               |               |

| Configurable Logic Cell (CLC)         CLC1       •         CLC2       •         CLC3       •         CLC3       •         Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)       •         EUSART       •         Master Synchronous Serial Ports       •         Op Amp       •         Op Amp       •         Op Amp 1       •         Op Amp 2       •         Pulse-Width Modulator (PWM)       •         Timers       Timer0       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              | C1          | •             | •             |

| CLC1       •         CLC2       •         CLC3       •         CLC3       •         Enhanced Universal Synchronous/Asynchronous         Receiver/Transmitter (EUSART)         EUSART       •         Master Synchronous Serial Ports         Op Amp         Op Amp 1       •         Pulse-Width Modulator (PWM)         PWM3       •         PWM4       •         Timers       Timer0       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              | C2          | ٠             | •             |

| CLC2•CLC3••CLC3••Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)•EUSART••Master Synchronous Serial Ports•Master Synchronous Serial Ports•Op Amp•Op Amp•Op Amp 1•Op Amp 2•Pulse-Width Modulator (PWM)•PWM3•Timers•Timer0•Timer1•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Configurable Logic Cell (CLC |             |               |               |

| CLC3•Enhanced Universal Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART)•EUSART••Master Synchronous Serial PortsMSSP•Op AmpMSSP••Op AmpOp Amp 1•Op Amp 2••Pulse-Width Modulator (PWM)••TimersTimer0••Timer1••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              | CLC1        | •             | •             |

| Enhanced Universal Synchronous/Asynchronous         Receiver/Transmitter (EUSART)         Master Synchronous Serial Ports         Master Synchronous Serial Ports         Op Amp         Op Amp 1         Op Amp 2         Pulse-Width Modulator (PWM)         PWM3         PWM4         Timers         Timer0         Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              | CLC2        | •             | •             |

| Receiver/Transmitter (EUSART)         EUSART       •       •         Master Synchronous Serial Ports       MSSP       •       •         Op Amp       Op Amp 1       •       •       •         Op Amp       Op Amp 1       •       •       •         Pulse-Width Modulator (PWM)       PWM3       •       •         Timers       Timer0       •       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              | CLC3        | ٠             | ٠             |

| Master Synchronous Serial Ports         MSSP       •         Op Amp       •         Op Amp 1       •       •         Op Amp 1       •       •         Op Amp 2       •       •         Pulse-Width Modulator (PWM)       PWM3       •         PWM4       •       •         Timers       Timer0       •         Timer1       •       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |             | nous          |               |

| MSSP         •         •           Op Amp         Op Amp 1         •         •           Op Amp 2         •         •         •           Pulse-Width Modulator (PWM)         PWM3         •         •           PWM3         •         •         •           Timers         Timer0         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              | EUSART      | ٠             | ٠             |

| Op Amp         Op Amp 1         Op Amp 2         Op Amp 2         Pulse-Width Modulator (PWM)         PWM3         PWM4         Timers         Timer1         Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Master Synchronous Serial I  | Ports       |               |               |

| Op Amp 1     •       Op Amp 2     •       Pulse-Width Modulator (PWM)       PWM3     •       PWM4     •       Timers       Timer1     •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              | MSSP        | ٠             | •             |

| Op Amp 2     •       Pulse-Width Modulator (PWM)       PWM3     •       PWM4     •       Timers       Timer0     •       Timer1     •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Op Amp                       |             |               |               |

| Pulse-Width Modulator (PWM)         PWM3       •         PWM4       •         Timers         Timer1       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              | Op Amp 1    | •             | •             |

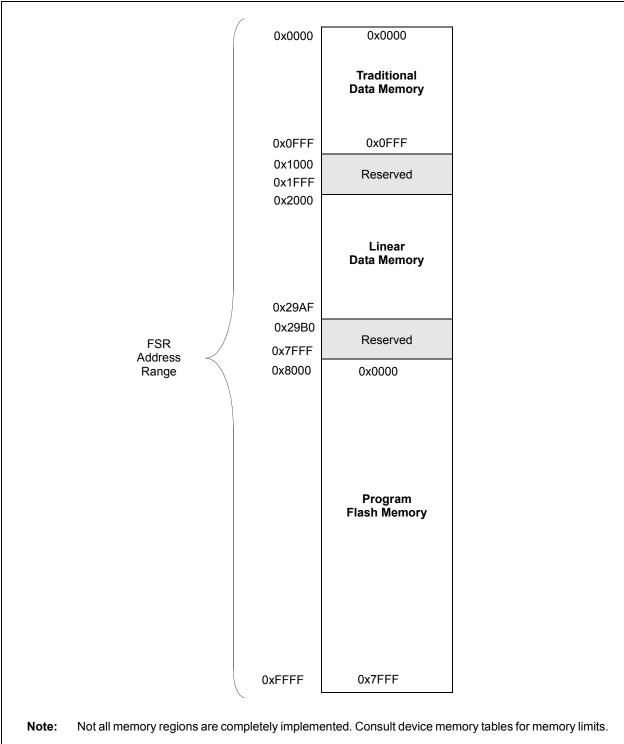

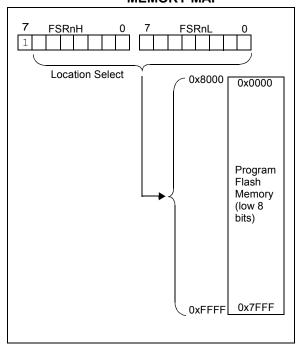

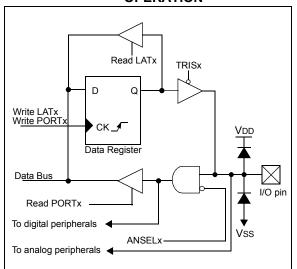

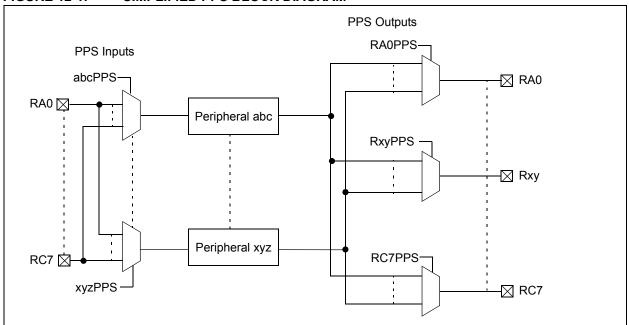

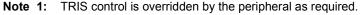

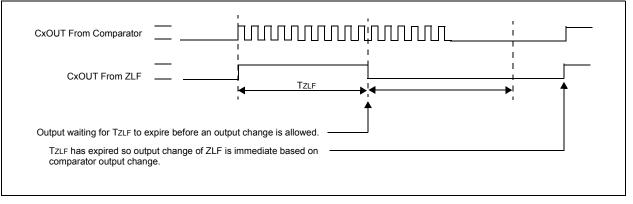

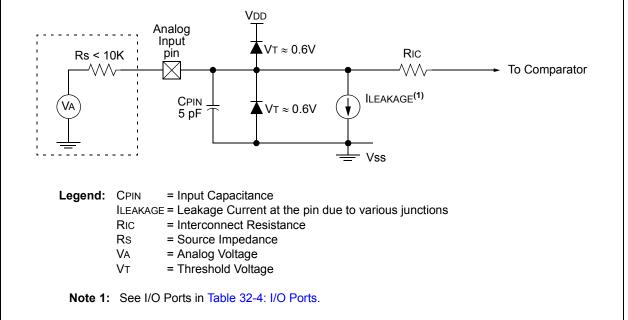

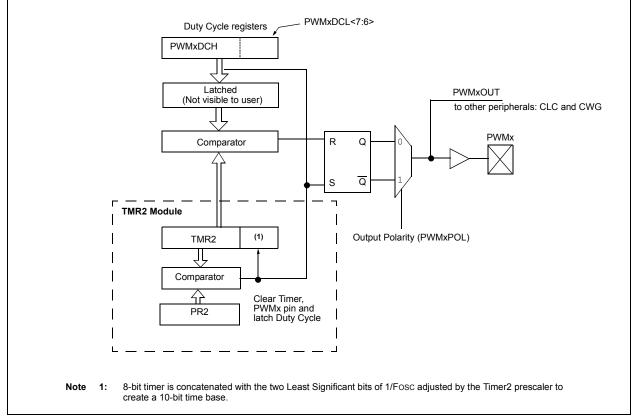

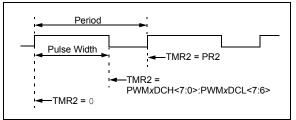

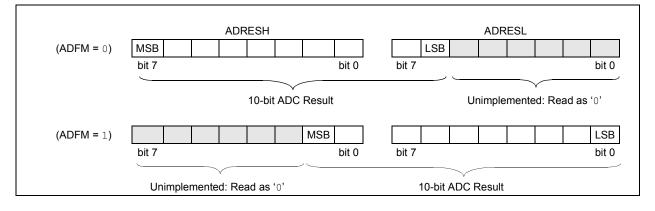

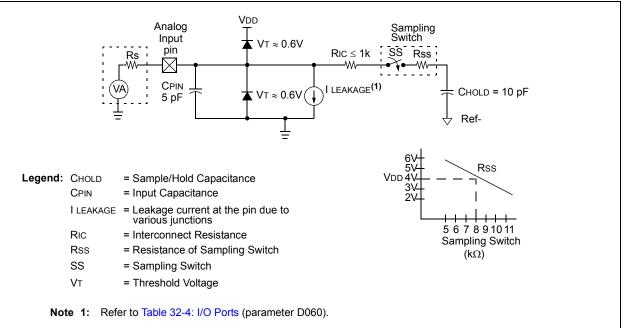

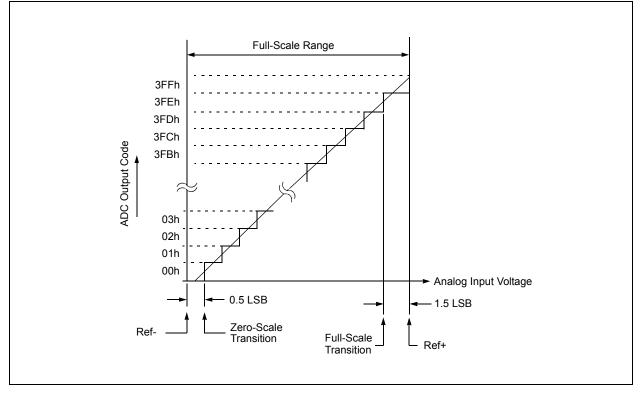

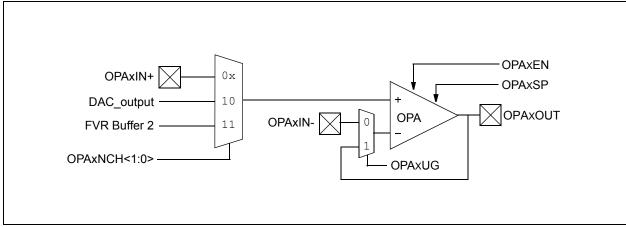

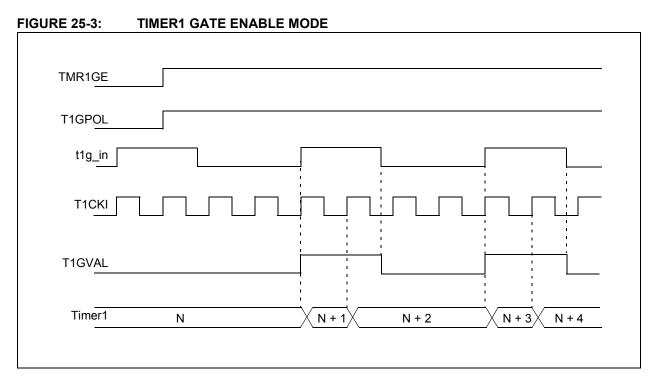

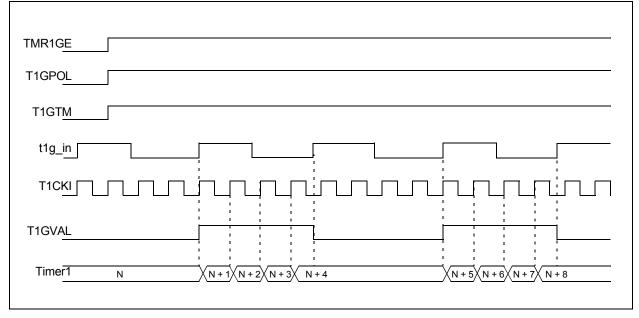

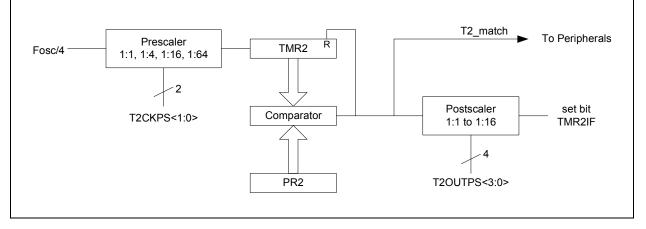

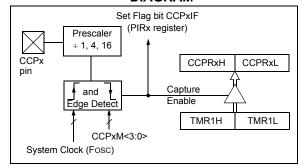

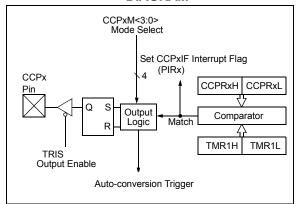

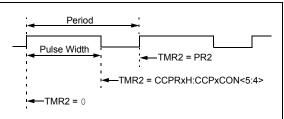

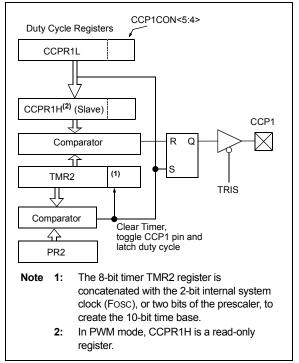

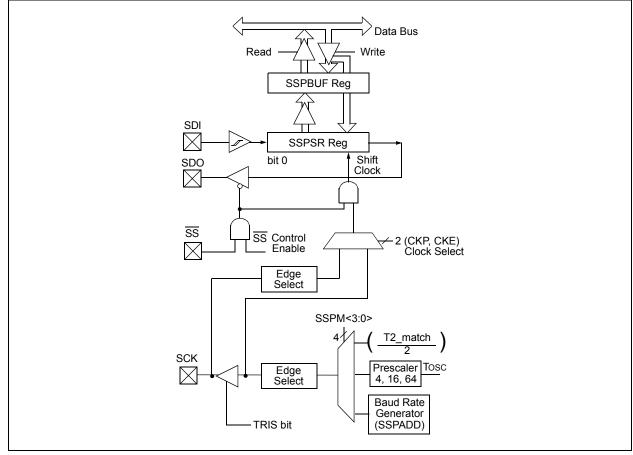

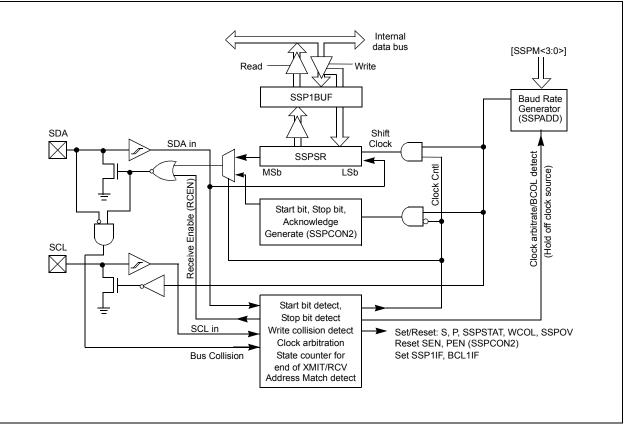

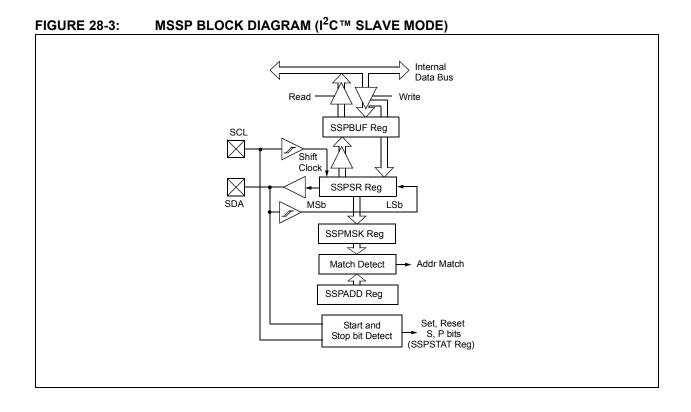

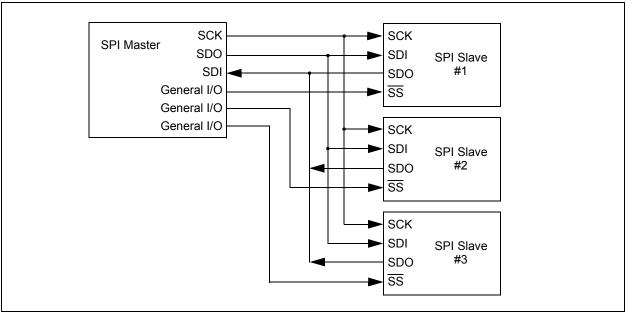

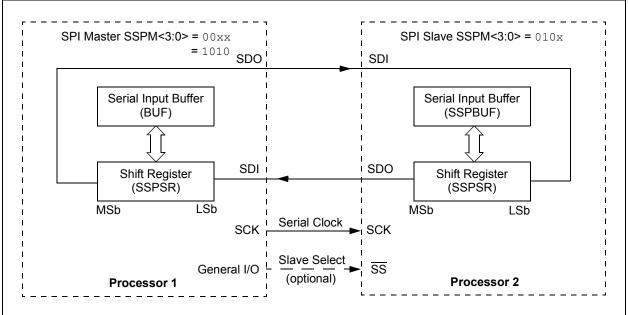

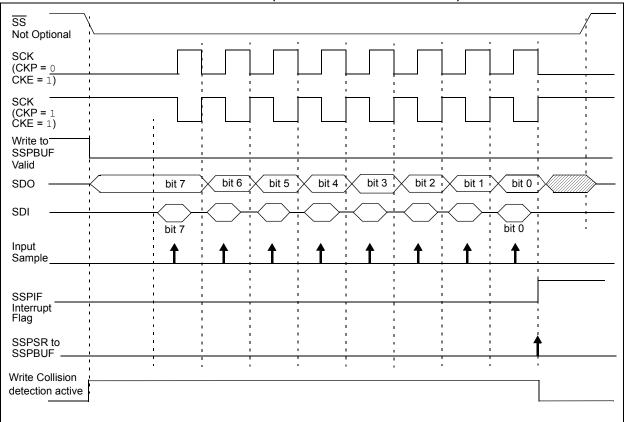

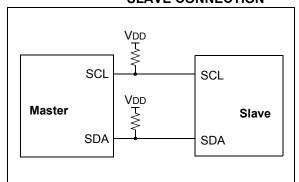

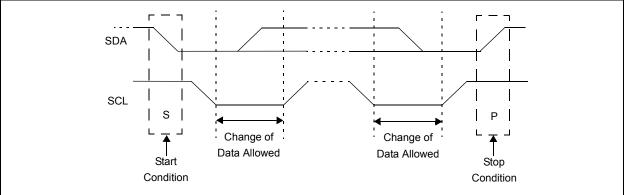

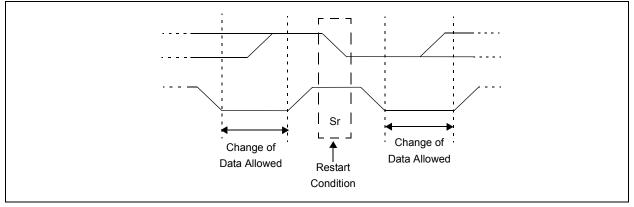

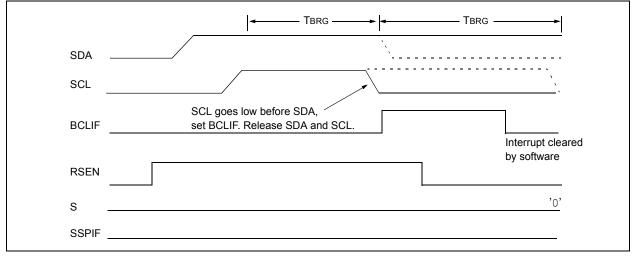

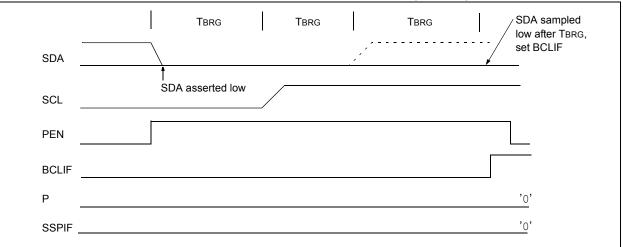

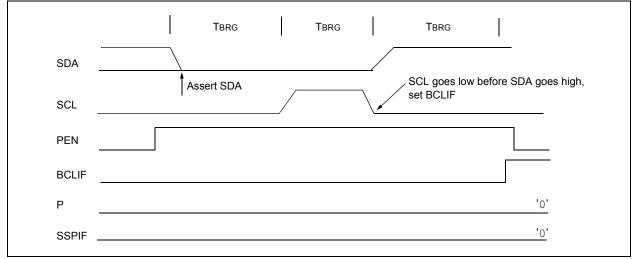

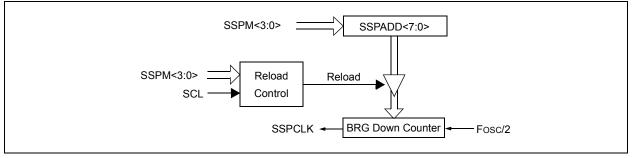

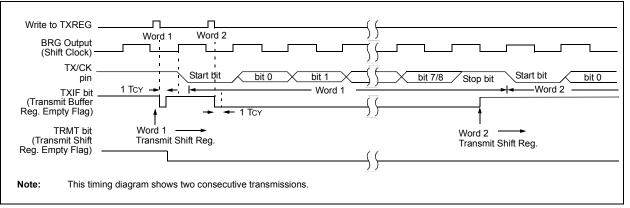

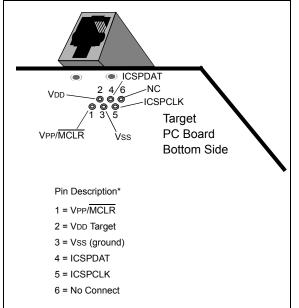

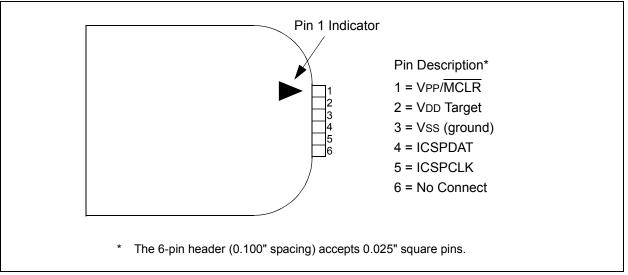

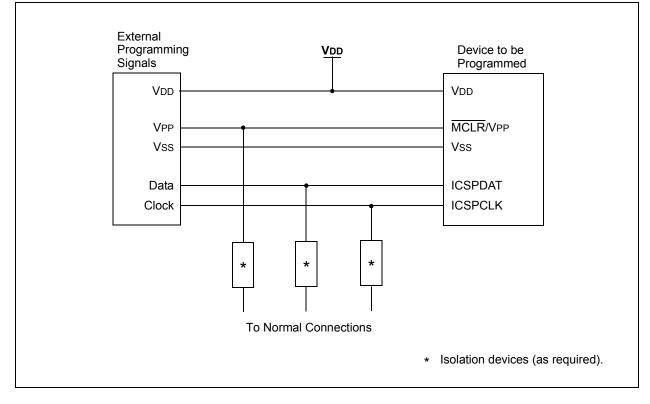

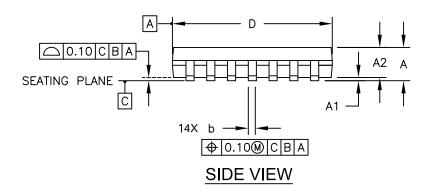

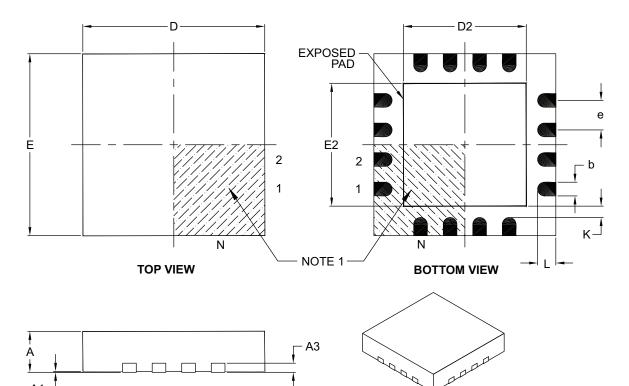

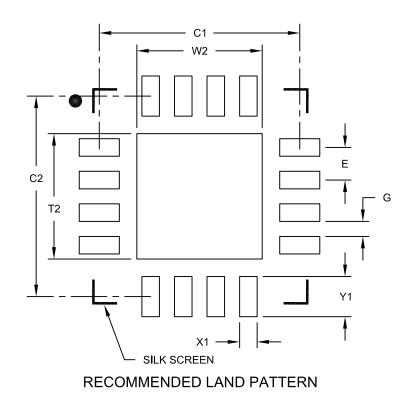

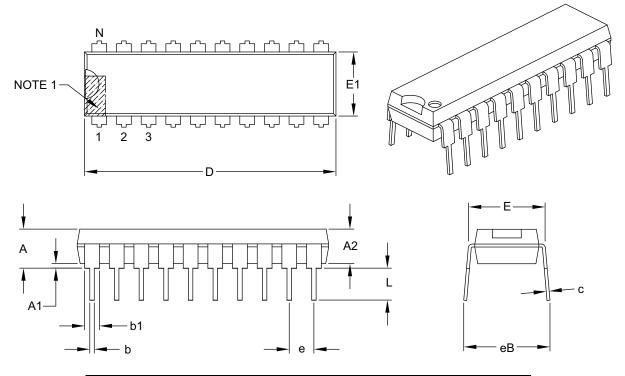

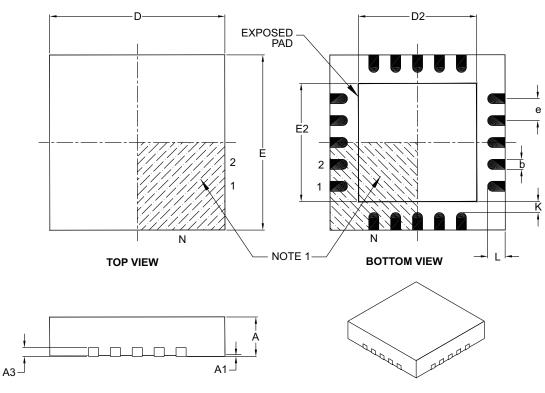

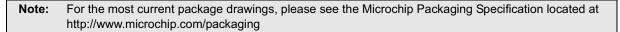

| PWM3         •           PWM4         •           Timers         •           Timer1         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              | Op Amp 2    | •             | •             |