## CAP1126

# **6 Channel Capacitive Touch Sensor** with 2 LED Drivers

#### PRODUCT FEATURES

**Datasheet**

#### **General Description**

The CAP1126, which incorporates SMSC's RightTouch® 1 technology, is a multiple channel Capacitive Touch sensor with multiple power LED drivers. It contains six (6) individual capacitive touch sensor inputs with programmable sensitivity for use in touch sensor applications. Each sensor input automatically recalibrates to compensate for gradual environmental changes.

The CAP1126 also contains two (2) LED drivers that offer full-on / off, variable rate blinking, dimness controls, and breathing. Each of the LED drivers may be linked to one of the sensor inputs to be actuated when a touch is detected. As well, each LED driver may be individually controlled via a host controller.

The CAP1126 includes Multiple Pattern Touch recognition that allows the user to select a specific set of buttons to be touched simultaneously. If this pattern is detected, then a status bit is set and an interrupt generated.

Additionally, the CAP1126 includes circuitry and support for enhanced sensor proximity detection.

The CAP1126 offers multiple power states operating at low quiescent currents. In the Standby state of operation, one or more capacitive touch sensor inputs are active and all LEDs may be used. If a touch is detected, it will wake the system using the WAKE/SPI\_MOSI pin.

Deep Sleep is the lowest power state available, drawing 5uA (typical) of current. In this state, no sensor inputs are active. Driving the WAKE/SPI\_MOSI pin or communications will wake the device.

## **Applications**

- Desktop and Notebook PCs

- LCD Monitors

- Consumer Electronics

- Appliances

#### **Features**

- Six (6) Capacitive Touch Sensor Inputs

- Programmable sensitivity

- Automatic recalibration

- Individual thresholds for each button

- Proximity Detection

- Multiple Button Pattern Detection

- Calibrates for Parasitic Capacitance

- Analog Filtering for System Noise Sources

- Press and Hold feature for Volume-like Applications

- Multiple Communication Interfaces

- SMBus / I<sup>2</sup>C compliant interface

- SMSC BC-Link interface

- SPI communications

- Pin selectable communications protocol and multiple slave addresses (SMBus / I<sup>2</sup>C only)

- Low Power Operation

- 5uA quiescent current in Deep Sleep

- 50uA quiescent current in Standby (1 sensor input monitored)

- Samples one or more channels in Standby

- Two (2) LED Driver Outputs

- Open Drain or Push-Pull

- Programmable blink, breathe, and dimness controls

- Can be linked to Capacitive Touch Sensor inputs

- Dedicated Wake output flags touches in low power state

- System RESET pin

- Available in 16-pin 4mm x 4mm RoHS compliant QFN package

### SMSC, the SMSC logo and RightTouch are registered trademarks and the RightTouch logo is a trademark of Standard Microsystems Corporation ("SMSC")

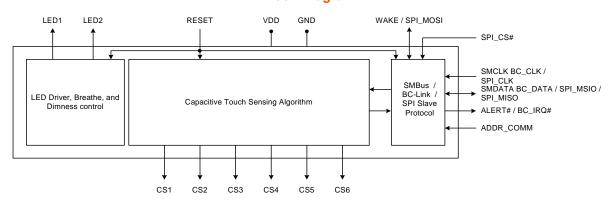

#### **Block Diagram**

#### Ordering Information:

| ORDERING NUMBER | PACKAGE                                            | FEATURES                                                                                                     |

|-----------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| CAP1126-1-AP-TR | 16-pin QFN 4mm x 4mm<br>(Lead-free RoHS compliant) | Six capacitive touch sensor inputs, Two LED drivers, Dedicated Wake, Reset, SMBus / BC-Link / SPI interfaces |

#### Reel size is 4,000 pieces

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Please contact your SMSC sales representative for additional documentation related to this product such as application notes, anomaly sheets, and design guidelines.

Copyright © 2012 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

The Microchip name and logo, and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chap | ter 1               | Pin Description                                | 10 |

|------|---------------------|------------------------------------------------|----|

| Chap | ter 2               | Electrical Specifications                      | 13 |

| Chap |                     | Communications                                 |    |

| 3.1  | Comm                | nunications                                    |    |

|      | 3.1.1               | SMBus (I <sup>2</sup> C) Communications        |    |

|      | 3.1.2               | SPI Communications                             |    |

|      | 3.1.3               | BC-Link Communications                         |    |

| 3.2  | Syster              | m Management Bus                               |    |

|      | 3.2.1               | SMBus Start Bit                                |    |

|      | 3.2.2               | SMBus Address and RD / WR Bit                  |    |

|      | 3.2.3               | SMBus Data Bytes                               |    |

|      | 3.2.4               | SMBus ACK and NACK Bits                        |    |

|      | 3.2.5               | SMBus Stop Bit                                 |    |

|      | 3.2.6               | SMBus Timeout                                  |    |

|      | 3.2.7               | SMBus and I <sup>2</sup> C Compatibility       |    |

| 3.3  | SMBu                | s Protocols                                    |    |

|      | 3.3.1               | SMBus Write Byte                               |    |

|      | 3.3.2               | SMBus Read Byte                                |    |

|      | 3.3.3               | SMBus Send Byte                                |    |

|      | 3.3.4               | SMBus Receive Byte                             |    |

| 3.4  | I <sup>2</sup> C Pr | otocols                                        | 21 |

|      | 3.4.1               | Block Write                                    |    |

|      | 3.4.2               | Block Read                                     |    |

| 3.5  | SPI In              | terface                                        |    |

|      | 3.5.1               | SPI Normal Mode                                |    |

|      | 3.5.2               | SPI Bi-Directional Mode                        | 22 |

|      | 3.5.3               | SPI_CS# Pin                                    | 22 |

|      | 3.5.4               | Address Pointer                                | 23 |

|      | 3.5.5               | SPI Timeout                                    | 23 |

| 3.6  | Norma               | al SPI Protocols                               | 23 |

|      | 3.6.1               | Reset Interface                                | 24 |

|      | 3.6.2               | Set Address Pointer                            | 25 |

|      | 3.6.3               | Write Data                                     | 25 |

|      | 3.6.4               | Read Data                                      |    |

| 3.7  | Bi-Dire             | ectional SPI Protocols                         | 27 |

|      | 3.7.1               | Reset Interface                                | 27 |

|      | 3.7.2               | Set Address Pointer                            | 27 |

|      | 3.7.3               | Write Data                                     | 28 |

|      | 3.7.4               | Read Data                                      | 28 |

| 3.8  | BC-Lir              | nk Interface                                   | 29 |

| -    |                     |                                                |    |

| Chap |                     | General Description                            |    |

| 4.1  |                     | States                                         |    |

| 4.2  |                     | T Pin                                          |    |

| 4.3  |                     | :/SPI_MOSI Pin Operation                       |    |

| 4.4  |                     | Orivers                                        |    |

|      | 4.4.1               | Linking LEDs to Capacitive Touch Sensor Inputs |    |

| 4.5  | Capac               | itive Touch Sensing                            | 33 |

|      | 4.5.1<br>4.5.2<br>4.5.3 | Sensing Cycle                          | 33 |

|------|-------------------------|----------------------------------------|----|

|      | 4.5.4                   | Multiple Touch Pattern Detection       |    |

|      | 4.5.5                   | Low Frequency Noise Detection          |    |

|      | 4.5.6                   | RF Noise Detection                     |    |

| 4.6  |                         | Pin                                    |    |

| 4.0  | 4.6.1                   | Sensor Interrupt Behavior              |    |

|      |                         | Concor interrupt Borianier :           | _  |

| Chap | oter 5 F                | Register Description                   | 37 |

| 5.1  | Main Co                 | ntrol Register                         | 41 |

| 5.2  | Status R                | egisters                               | 42 |

|      | 5.2.1                   | General Status - 02h                   | 42 |

|      | 5.2.2                   | Sensor Input Status - 03h              | 42 |

|      | 5.2.3                   | LED Status - 04h                       | 43 |

| 5.3  | Noise Fla               | ag Status Registers                    | 43 |

| 5.4  | Sensor I                | nput Delta Count Registers             | 44 |

| 5.5  | Sensitivi               | ty Control Register                    | 44 |

| 5.6  | Configur                | ation Registers                        | 46 |

|      | 5.6.1                   | Configuration - 20h                    |    |

|      | 5.6.2                   | Configuration 2 - 44h                  | 47 |

| 5.7  | Sensor I                | nput Enable Registers                  | 48 |

| 5.8  | Sensor I                | nput Configuration Register            | 48 |

| 5.9  |                         | nput Configuration 2 Register          |    |

| 5.10 | Averagin                | ng and Sampling Configuration Register | 51 |

| 5.11 | Calibration             | on Activate Register                   | 53 |

| 5.12 | Interrupt               | Enable Register                        | 53 |

| 5.13 |                         | Rate Enable Register                   |    |

| 5.14 |                         | Touch Configuration Register           |    |

| 5.15 |                         | Touch Pattern Configuration Register   |    |

| 5.16 |                         | Touch Pattern Register                 |    |

| 5.17 |                         | ation Configuration Register           |    |

| 5.18 |                         | nput Threshold Registers               |    |

| 5.19 |                         | nput Noise Threshold Register          |    |

| 5.20 |                         | Channel Register                       |    |

| 5.21 |                         | Configuration Register                 |    |

| 5.22 | ,                       | Sensitivity Register                   |    |

| 5.23 |                         | Threshold Register                     |    |

| 5.24 |                         | nput Base Count Registers              |    |

| 5.25 |                         | put Type Register                      |    |

| 5.26 |                         | nput LED Linking Register              |    |

| 5.27 |                         | arity Register                         |    |

| 5.28 |                         | put Control Register                   |    |

| 5.29 |                         | ED Transition Control Register         |    |

| 5.30 |                         | ror Control Register                   |    |

| 5.31 |                         | navior Register                        |    |

| 5.32 |                         | se 1 Period Register                   |    |

| 5.33 |                         | se 2 Period Register                   |    |

| 5.34 |                         | athe Period Register                   |    |

| 5.35 |                         | nfiguration Register                   |    |

| 5.36 |                         | y Cycle Registers                      |    |

| 5.37 |                         | ect Ramp Rates Register                |    |

| 5.38 |                         | Delay Register                         |    |

| 5.39 | Sensor I                | nput Calibration Registers             | 80 |

| 5.41     | Product ID Register               | . 8  |

|----------|-----------------------------------|------|

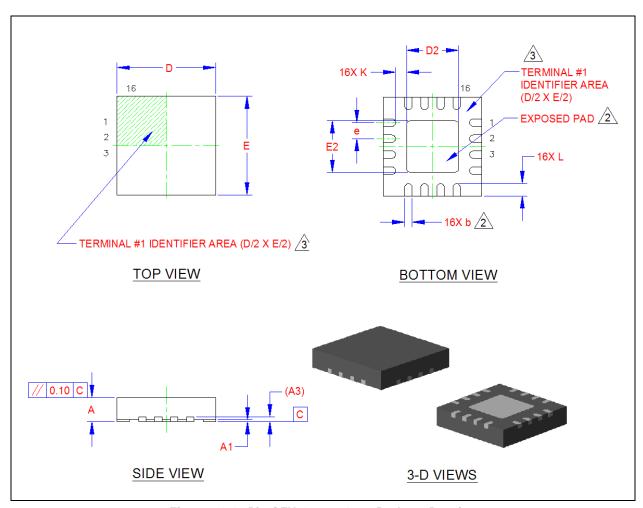

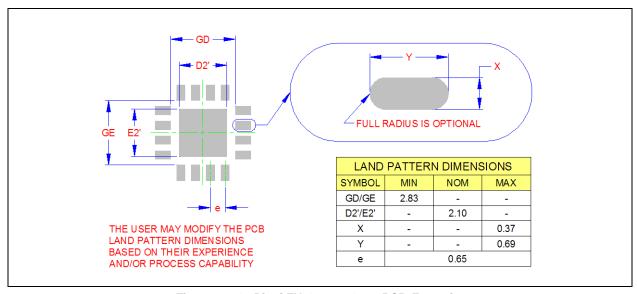

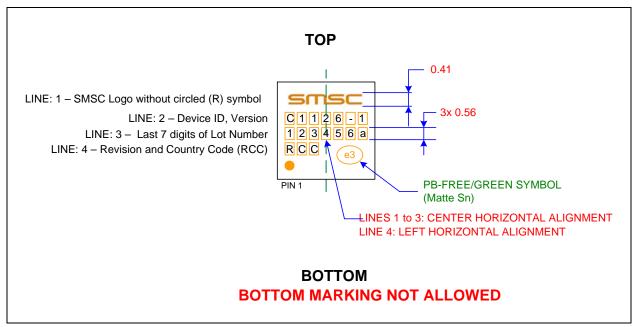

| Char     | oter 6 Package Information        | . 82 |

| _        | CAP1126 Package Drawings          |      |

| 6.2      | Package Marking                   | . 84 |

| Appe     | endix A Device Delta              | . 85 |

|          | Delta from CAP1026 to CAP1126     |      |

| <br>Char | oter 7 Datasheet Revision History | . 87 |

# **List of Figures**

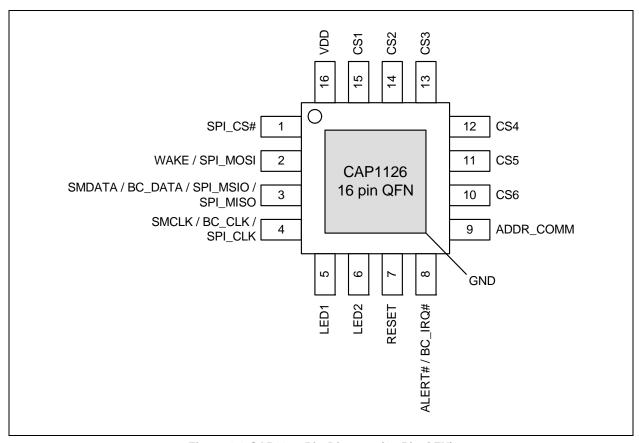

| Figure 1.1  | CAP1126 Pin Diagram (16-Pin QFN)                      | . 10 |

|-------------|-------------------------------------------------------|------|

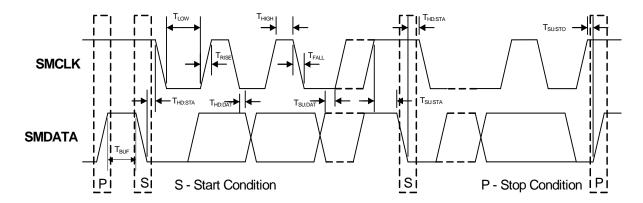

| Figure 3.1  | SMBus Timing Diagram                                  | . 18 |

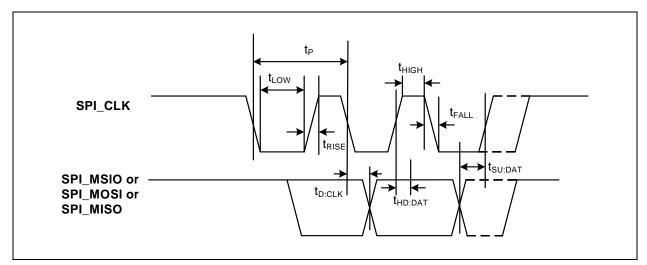

| Figure 3.2  | SPI Timing                                            | . 22 |

| Figure 3.3  | Example SPI Bus Communication - Normal Mode           | . 24 |

| Figure 3.4  | SPI Reset Interface Command - Normal Mode             | . 25 |

| Figure 3.5  | SPI Set Address Pointer Command - Normal Mode         | . 25 |

| Figure 3.6  | SPI Write Command - Normal Mode                       | . 26 |

| Figure 3.7  | SPI Read Command - Normal Mode                        | . 26 |

| Figure 3.8  | SPI Read Command - Normal Mode - Full                 | . 27 |

| Figure 3.9  | SPI Reset Interface Command - Bi-directional Mode     | . 27 |

| Figure 3.10 | SPI Set Address Pointer Command - Bi-directional Mode | . 28 |

| Figure 3.11 | SPI Write Data Command - Bi-directional Mode          | . 28 |

| Figure 3.12 | SPI Read Data Command - Bi-directional Mode           | . 28 |

| Figure 4.1  | System Diagram for CAP1126                            | . 31 |

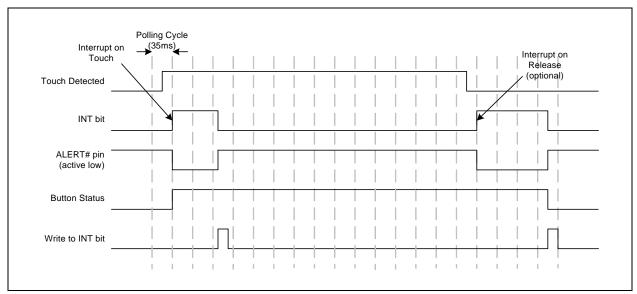

| Figure 4.2  | Sensor Interrupt Behavior - Repeat Rate Enabled       | . 35 |

| Figure 4.3  | Sensor Interrupt Behavior - No Repeat Rate Enabled    | . 36 |

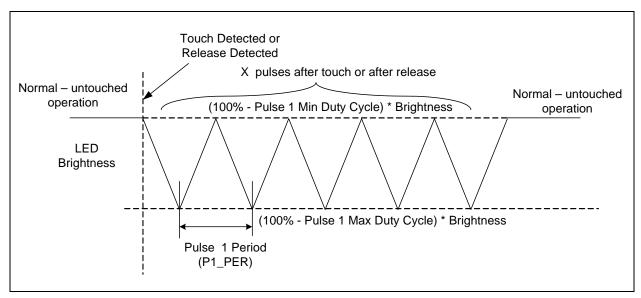

| Figure 5.1  | Pulse 1 Behavior with Non-Inverted Polarity           |      |

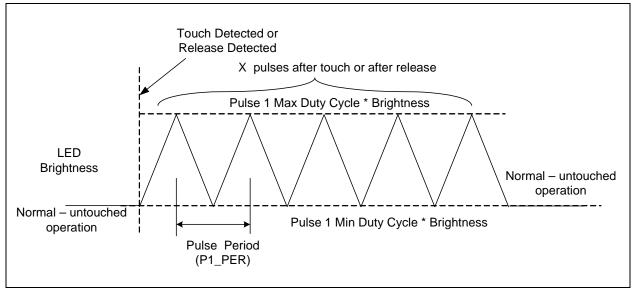

| Figure 5.2  | Pulse 1 Behavior with Inverted Polarity               | . 71 |

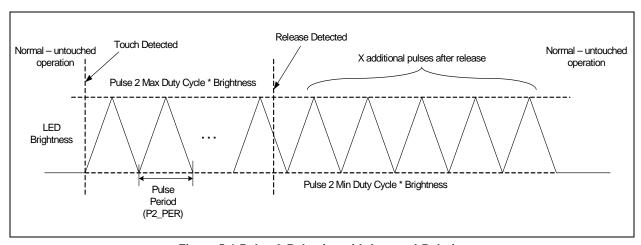

| Figure 5.3  | Pulse 2 Behavior with Non-Inverted Polarity           | . 73 |

| Figure 5.4  | Pulse 2 Behavior with Inverted Polarity               | . 73 |

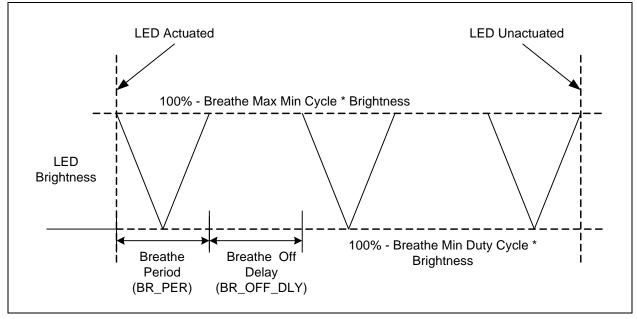

| Figure 5.5  | Breathe Behavior with Non-Inverted Polarity           | . 77 |

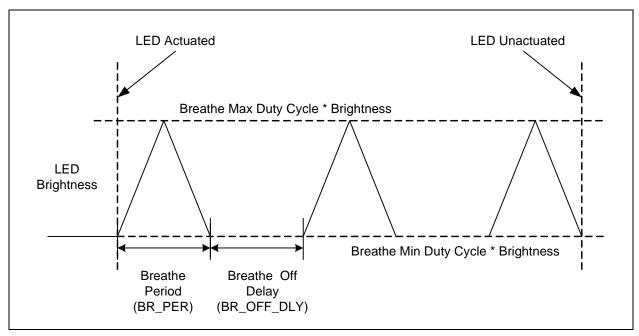

| Figure 5.6  | Breathe Behavior with Inverted Polarity               | . 78 |

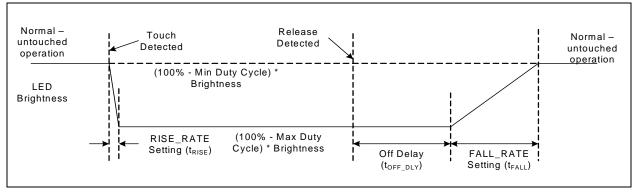

| Figure 5.7  | Direct Behavior for Non-Inverted Polarity             | . 79 |

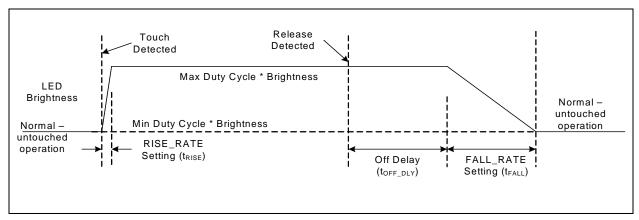

| Figure 5.8  | Direct Behavior for Inverted Polarity                 | . 79 |

| Figure 6.1  | 16-Pin QFN 4mm x 4mm Package Drawing                  | . 82 |

| Figure 6.2  | 16-Pin QFN 4mm x 4mm Package Dimensions               | . 83 |

| Figure 6.3  | 16-Pin QFN 4mm x 4mm PCB Footprint                    |      |

| Figure 6.4  | CAP1126 Package Markings                              | . 84 |

# **List of Tables**

| Table 1.1  | Pin Description for CAP1126                   |    |

|------------|-----------------------------------------------|----|

| Table 1.2  | Pin Types                                     |    |

| Table 2.1  | Absolute Maximum Ratings                      |    |

| Table 2.2  | Electrical Specifications                     |    |

| Table 3.1  | ADDR_COMM Pin Decode                          |    |

| Table 3.2  | Protocol Format                               | 19 |

| Table 3.3  | Write Byte Protocol                           | 20 |

| Table 3.4  | Read Byte Protocol                            | 20 |

| Table 3.5  | Send Byte Protocol                            | 20 |

| Table 3.6  | Receive Byte Protocol                         | 20 |

| Table 3.7  | Block Write Protocol                          | 21 |

| Table 3.8  | Block Read Protocol                           |    |

| Table 5.1  | Register Set in Hexadecimal Order             | 37 |

| Table 5.2  | Main Control Register                         | 41 |

| Table 5.3  | GAIN Bit Decode                               | 41 |

| Table 5.4  | Status Registers                              | 42 |

| Table 5.5  | Noise Flag Status Registers                   | 43 |

| Table 5.6  | Sensor Input Delta Count Registers            | 44 |

| Table 5.7  | Sensitivity Control Register                  |    |

| Table 5.8  | DELTA_SENSE Bit Decode                        | 45 |

| Table 5.9  | BASE_SHIFT Bit Decode                         | 45 |

| Table 5.10 | Configuration Registers                       | 46 |

| Table 5.11 | Sensor Input Enable Registers                 |    |

| Table 5.12 | Sensor Input Configuration Register           |    |

| Table 5.13 | MAX_DUR Bit Decode                            |    |

| Table 5.14 | RPT_RATE Bit Decode                           |    |

| Table 5.15 | Sensor Input Configuration 2 Register         |    |

| Table 5.16 | M_PRESS Bit Decode                            |    |

| Table 5.17 | Averaging and Sampling Configuration Register | 51 |

| Table 5.18 | AVG Bit Decode                                | 51 |

| Table 5.19 | SAMP_TIME Bit Decode                          | 52 |

| Table 5.20 | CYCLE_TIME Bit Decode                         | 52 |

| Table 5.21 | Calibration Activate Register                 | 53 |

| Table 5.22 | Interrupt Enable Register                     | 53 |

| Table 5.23 | Repeat Rate Enable Register                   | 54 |

| Table 5.24 | Multiple Touch Configuration                  | 54 |

| Table 5.25 | B_MULT_T Bit Decode                           | 55 |

| Table 5.26 | Multiple Touch Pattern Configuration          | 55 |

| Table 5.27 | MTP_TH Bit Decode                             | 56 |

| Table 5.28 | Multiple Touch Pattern Register               | 56 |

| Table 5.29 | Recalibration Configuration Registers         | 57 |

| Table 5.30 | NEG_DELTA_CNT Bit Decode                      | 58 |

| Table 5.31 | CAL_CFG Bit Decode                            | 58 |

| Table 5.32 | Sensor Input Threshold Registers              | 59 |

| Table 5.33 | Sensor Input Noise Threshold Register         |    |

| Table 5.34 | CSx_BN_TH Bit Decode                          | 60 |

| Table 5.35 | Standby Channel Register                      |    |

| Table 5.36 | Standby Configuration Register                |    |

| Table 5.37 | STBY_AVG Bit Decode                           |    |

| Table 5.38 | STBY_SAMP_TIME Bit Decode                     | 61 |

| Table 5.39 | STBY_CY_TIME Bit Decode                       |    |

| Table 5.40 | Standby Sensitivity Register                  |    |

| Table 5.41 | STBY_SENSE Bit Decode                  | . 63 |

|------------|----------------------------------------|------|

| Table 5.42 | Standby Threshold Register             |      |

| Table 5.43 | Sensor Input Base Count Registers      | . 63 |

| Table 5.44 | LED Output Type Register               |      |

| Table 5.45 | Sensor Input LED Linking Register      | . 64 |

| Table 5.46 | LED Polarity Register                  | . 65 |

| Table 5.47 | LED Output Control Register            | . 66 |

| Table 5.48 | LED Polarity Behavior                  | . 67 |

| Table 5.49 | Linked LED Transition Control Register | . 67 |

| Table 5.50 | LED Mirror Control Register            | . 68 |

| Table 5.51 | LED Behavior Register                  | . 68 |

| Table 5.52 | LEDx_CTL Bit Decode                    |      |

| Table 5.53 | LED Pulse 1 Period Register            | . 70 |

| Table 5.54 | LED Pulse / Breathe Period Example     | . 72 |

| Table 5.55 | LED Pulse 2 Period Register            | . 72 |

| Table 5.56 | LED Breathe Period Register            | . 73 |

| Table 5.57 | LED Configuration Register             | . 74 |

| Table 5.58 | PULSEX_CNT Decode                      | . 74 |

| Table 5.59 | LED Duty Cycle Registers               | . 75 |

| Table 5.60 | LED Duty Cycle Decode                  | . 75 |

| Table 5.61 | LED Direct Ramp Rates Register         | . 76 |

| Table 5.62 | Rise / Fall Rate Decode                | . 76 |

| Table 5.63 | LED Off Delay Register                 | . 77 |

| Table 5.64 | Breathe Off Delay Settings             | . 78 |

| Table 5.65 | Off Delay Decode                       | . 79 |

| Table 5.66 | Sensor Input Calibration Registers     | . 80 |

| Table 5.67 | Product ID Register                    | . 81 |

| Table 5.68 | Vendor ID Register                     | . 81 |

| Table 5.69 | Revision Register                      |      |

| Table A.1  | Register Delta From CAP1026 to CAP1126 | . 85 |

| Table 7.1  | Customer Revision History              | . 87 |

# **Chapter 1 Pin Description**

Figure 1.1 CAP1126 Pin Diagram (16-Pin QFN)

Table 1.1 Pin Description for CAP1126

| PIN<br>NUMBER | PIN NAME           | PIN FUNCTION                                                                                    | PIN TYPE | UNUSED CONNECTION    |

|---------------|--------------------|-------------------------------------------------------------------------------------------------|----------|----------------------|

| 1             | SPI_CS#            | Active low chip-select for SPI bus                                                              | DI (5V)  | Connect to<br>Ground |

|               |                    | WAKE - Active high wake / interrupt output<br>Standby power state - requires pull-down resistor | DO       | Pull-down            |

| 2             | WAKE /<br>SPI_MOSI | WAKE - Active high wake input - requires pull-down resistor Deep Sleep power state              | DI       | Resistor             |

|               |                    | SPI_MOSI - SPI Master-Out-Slave-In port when used in normal mode                                | DI (5V)  | Connect to<br>Ground |

Table 1.1 Pin Description for CAP1126 (continued)

| PIN<br>NUMBER | PIN NAME               | PIN FUNCTION                                                                                                | PIN TYPE  | UNUSED CONNECTION                     |

|---------------|------------------------|-------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|

|               | SMDATA /<br>BC_DATA /  | SMDATA - Bi-directional, open-drain SMBus data - requires pull-up resistor                                  | DIOD (5V) |                                       |

| 3             |                        | BC_DATA - Bi-directional, open-drain BC-Link data - requires pull-up resistor                               | DIO       | n/a                                   |

|               | SPI_MSIO /<br>SPI_MISO | SPI_MSIO - SPI Master-Slave-In-Out bidirectional port when used in bi-directional mode                      | DIO       | 11/4                                  |

|               |                        | SPI_MISO - SPI Master-In-Slave-Out port when used in normal mode                                            | DO        |                                       |

|               | SMCLK /                | SMCLK - SMBus clock input - requires pull-up resistor                                                       | DI (5V)   |                                       |

| 4             | BC_CLK /<br>SPI_CLK    | BC_CLK - BC-Link clock input                                                                                | DI (5V)   | n/a                                   |

|               | SFI_CLK                | SPI_CLK - SPI clock input                                                                                   | DI (5V)   |                                       |

|               |                        | Open drain LED 1 driver (default)                                                                           | OD (5V)   | Connect to<br>Ground                  |

| 5             | LED1                   | Push-pull LED 1 driver                                                                                      | DO        | leave open or<br>connect to<br>Ground |

|               |                        | Open drain LED 2 driver (default)                                                                           | OD (5V)   | Connect to<br>Ground                  |

| 6             | LED2                   | Push-pull LED 2 driver                                                                                      | DO        | leave open or connect to Ground       |

| 7             | RESET                  | Active high soft reset for system - resets all registers to default values. If not used, connect to ground. | DI (5V)   | Connect to<br>Ground                  |

|               |                        | ALERT# - Active low alert / interrupt output for SMBus alert or SPI interrupt                               | OD (5V)   | Connect to<br>Ground                  |

| 8             | ALERT# /               | ALERT# - Active high push-pull alert / interrupt output for SMBus alert or SPI interrupt                    | DO        | leave open                            |

|               | BC_IRQ#                | BC_IRQ# - Active low interrupt / optional for BC-Link                                                       | OD (5V)   | Connect to<br>Ground                  |

|               |                        | BC_IRQ# - Active high push-pull interrupt / optional for BC-Link                                            | DO        | leave open                            |

| 9             | ADDR_COMM              | Address / communications select pin - pull-down resistor determines address / communications mechanism      | AI        | n/a                                   |

| 10            | CS6                    | Capacitive Touch Sensor Input 6                                                                             | AIO       | Connect to<br>Ground                  |

| 11            | CS5                    | Capacitive Touch Sensor Input 5                                                                             | AIO       | Connect to<br>Ground                  |

| 12            | CS4                    | Capacitive Touch Sensor Input 4                                                                             | AIO       | Connect to<br>Ground                  |

| 13            | CS3                    | Capacitive Touch Sensor Input 3                                                                             | AIO       | Connect to<br>Ground                  |

Table 1.1 Pin Description for CAP1126 (continued)

| PIN<br>NUMBER | PIN NAME | PIN FUNCTION                    | PIN TYPE | UNUSED CONNECTION    |

|---------------|----------|---------------------------------|----------|----------------------|

| 14            | CS2      | Capacitive Touch Sensor Input 2 | AIO      | Connect to<br>Ground |

| 15            | CS1      | Capacitive Touch Sensor Input 1 | AIO      | Connect to<br>Ground |

| 16            | VDD      | Positive Power supply           | Power    | n/a                  |

| Bottom<br>Pad | GND      | Ground                          | Power    | n/a                  |

**APPLICATION NOTE:** When the ALERT# pin is configured as an active low output, it will be open drain. When it is configured as an active high output, it will be push-pull.

**APPLICATION NOTE:** For the 5V tolerant pins that have a pull-up resistor, the pull-up voltage must not exceed 3.6V when the CAP1126 is unpowered.

**APPLICATION NOTE:** The SPI\_CS# pin should be grounded when SMBus,  $I^2C$ , or BC-Link communications are used.

The pin types are described in Table 1.2. All pins labeled with (5V) are 5V tolerant.

Table 1.2 Pin Types

| PIN TYPE | DESCRIPTION                                                                                                                                                                     |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power    | This pin is used to supply power or ground to the device.                                                                                                                       |  |

| DI       | Digital Input - This pin is used as a digital input. This pin is 5V tolerant.                                                                                                   |  |

| AIO      | Analog Input / Output -This pin is used as an I/O for analog signals.                                                                                                           |  |

| DIOD     | Digital Input / Open Drain Output - This pin is used as a digital I/O. When it is used as an output, it is open drain and requires a pull-up resistor. This pin is 5V tolerant. |  |

| OD       | Open Drain Digital Output - This pin is used as a digital output. It is open drain and requires a pull-up resistor. This pin is 5V tolerant.                                    |  |

| DO       | Push-pull Digital Output - This pin is used as a digital output and can sink and source current.                                                                                |  |

| DIO      | Push-pull Digital Input / Output - This pin is used as an I/O for digital signals.                                                                                              |  |

# **Chapter 2 Electrical Specifications**

**Table 2.1 Absolute Maximum Ratings**

| Voltage on 5V tolerant pins (V <sub>5VT_PIN</sub> )                                 | -0.3 to 5.5       | V    |

|-------------------------------------------------------------------------------------|-------------------|------|

| Voltage on 5V tolerant pins ( V <sub>5VT_PIN</sub> - V <sub>DD</sub>  ) Note 2.2    | 0 to 3.6          | V    |

| Voltage on VDD pin                                                                  | -0.3 to 4         | V    |

| Voltage on any other pin to GND                                                     | -0.3 to VDD + 0.3 | V    |

| Package Power Dissipation up to T <sub>A</sub> = 85°C for 16 pin QFN (see Note 2.3) | 0.9               | W    |

| Junction to Ambient ( $\theta_{JA}$ ) (see Note 2.4)                                | 58                | °C/W |

| Operating Ambient Temperature Range                                                 | -40 to 125        | °C   |

| Storage Temperature Range                                                           | -55 to 150        | °C   |

| ESD Rating, All Pins, HBM                                                           | 8000              | V    |

- **Note 2.1** Stresses above those listed could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied.

- Note 2.2 For the 5V tolerant pins that have a pull-up resistor, the voltage difference between  $V_{5VT\_PIN}$  and  $V_{DD}$  must never exceed 3.6V.

- Note 2.3 The Package Power Dissipation specification assumes a recommended thermal via design consisting of a 3x3 matrix of 0.3mm (12mil) vias at 1.0mm pitch connected to the ground plane with a 2.1mm x 2.1mm thermal landing.

- Note 2.4 Junction to Ambient  $(\theta_{JA})$  is dependent on the design of the thermal vias. Without thermal vias and a thermal landing, the  $\theta_{JA}$  is approximately 60°C/W including localized PCB temperature increase.

**Table 2.2 Electrical Specifications**

| $V_{DD}$ = 3V to 3.6V, $T_A$ = 0°C to 85°C, all Typical values at $T_A$ = 27°C unless otherwise noted. |          |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|--|--|

| CHARACTERISTIC SYMBOL MIN TYP MAX UNIT CONDITIONS                                                      |          |  |  |  |  |  |  |  |  |  |  |

|                                                                                                        | DC Power |  |  |  |  |  |  |  |  |  |  |

| Supply Voltage V <sub>DD</sub> 3.0 3.3 3.6 V                                                           |          |  |  |  |  |  |  |  |  |  |  |

**Table 2.2 Electrical Specifications (continued)**

| V <sub>DD</sub> = 3V to                | 3.6V, T <sub>A</sub> = 0°   | C to 85°C, | all Typical | values at | T <sub>A</sub> = 27°C | unless otherwise noted.                                                                                                               |  |  |  |  |  |

|----------------------------------------|-----------------------------|------------|-------------|-----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CHARACTERISTIC                         | SYMBOL                      | MIN        | TYP         | MAX       | UNIT                  | CONDITIONS                                                                                                                            |  |  |  |  |  |

| Supply Current                         | I <sub>STBY</sub>           |            | 120         | 170       | uA                    | Standby state active 1 sensor input monitored No LEDs active Default conditions (8 avg, 70ms cycle time)                              |  |  |  |  |  |

|                                        | I <sub>STBY</sub>           |            | 50          |           | uA                    | Standby state active 1 sensor input monitored No LEDs active 1 avg, 140ms cycle time,                                                 |  |  |  |  |  |

|                                        | I <sub>DSLEEP</sub>         |            | 5           | 15        | uA                    | Deep Sleep state active LEDs at 100% or 0% Duty Cycle No communications $T_{A} < 40^{\circ}\text{C}$ $3.135 < V_{DD} < 3.465\text{V}$ |  |  |  |  |  |

|                                        | I <sub>DD</sub>             |            | 500         | 600       | uA                    | Capacitive Sensing Active<br>No LEDs active                                                                                           |  |  |  |  |  |

| Capacitive Touch Sensor Inputs         |                             |            |             |           |                       |                                                                                                                                       |  |  |  |  |  |

| Maximum Base<br>Capacitance            | C <sub>BASE</sub>           |            | 50          |           | pF                    | Pad untouched                                                                                                                         |  |  |  |  |  |

| Minimum Detectable<br>Capacitive Shift | $\Delta$ C <sub>TOUCH</sub> | 20         |             |           | fF                    | Pad touched - default conditions<br>(1 avg, 35ms cycle time, 1x<br>sensitivity)                                                       |  |  |  |  |  |

| Recommended Cap<br>Shift               | $\Delta c_{TOUCH}$          | 0.1        |             | 2         | pF                    | Pad touched - Not tested                                                                                                              |  |  |  |  |  |

| Power Supply<br>Rejection              | PSR                         |            | ±3          | ±10       | counts<br>/ V         | Untouched Current Counts Base Capacitance 5pF - 50pF Maximum sensitivity Negative Delta Counts disabled All other parameters default  |  |  |  |  |  |

|                                        | 1                           |            | Timir       | ng        | •                     |                                                                                                                                       |  |  |  |  |  |

| RESET Pin Delay                        | t <sub>RST_DLY</sub>        | 10         |             |           | ms                    |                                                                                                                                       |  |  |  |  |  |

| Time to communications ready           | tCOMM_DLY                   |            |             | 15        | ms                    |                                                                                                                                       |  |  |  |  |  |

| Time to first conversion ready         | t <sub>CONV_DLY</sub>       |            | 170         | 200       | ms                    |                                                                                                                                       |  |  |  |  |  |

|                                        |                             |            | LED Dr      | rivers    |                       |                                                                                                                                       |  |  |  |  |  |

| Duty Cycle                             | DUTY <sub>LED</sub>         | 0          |             | 100       | %                     | Programmable                                                                                                                          |  |  |  |  |  |

| Drive Frequency                        | f <sub>LED</sub>            |            | 2           |           | kHz                   |                                                                                                                                       |  |  |  |  |  |

| Sinking Current                        | I <sub>SINK</sub>           |            |             | 24        | mA                    | V <sub>OL</sub> = 0.4                                                                                                                 |  |  |  |  |  |

| Sourcing Current                       | I <sub>SOURCE</sub>         |            |             | 24        | mA                    | V <sub>OH</sub> = V <sub>DD</sub> - 0.4                                                                                               |  |  |  |  |  |

**Table 2.2 Electrical Specifications (continued)**

| $V_{DD} = 3V \text{ to}$              | 3.6V, T <sub>A</sub> = 0° | °C to 85°C,              | all Typical | values at | T <sub>A</sub> = 27°C | unless otherwise noted.                                                           |

|---------------------------------------|---------------------------|--------------------------|-------------|-----------|-----------------------|-----------------------------------------------------------------------------------|

| CHARACTERISTIC                        | SYMBOL                    | MIN                      | TYP         | MAX       | UNIT                  | CONDITIONS                                                                        |

| Leakage Current                       | I <sub>LEAK</sub>         |                          |             | ±5        | uA                    | powered or unpowered<br>TA < 85°C<br>pull-up voltage ≤ 3.6V if<br>unpowered       |

|                                       |                           |                          | I/O P       | ins       |                       |                                                                                   |

| Output Low Voltage                    | V <sub>OL</sub>           |                          |             | 0.4       | V                     | I <sub>SINK_IO</sub> = 8mA                                                        |

| Output High Voltage                   | V <sub>OH</sub>           | V <sub>DD</sub> -<br>0.4 |             |           | V                     | I <sub>SOURCE_IO</sub> = 8mA                                                      |

| Input High Voltage                    | V <sub>IH</sub>           | 2.0                      |             |           | V                     |                                                                                   |

| Input Low Voltage                     | V <sub>IL</sub>           |                          |             | 0.8       | V                     |                                                                                   |

| Leakage Current                       | I <sub>LEAK</sub>         |                          |             | ±5        | uA                    | powered or unpowered $T_A < 85^{\circ}C$ pull-up voltage $\leq 3.6V$ if unpowered |

| RESET Pin Release to conversion ready | t <sub>RESET</sub>        |                          | 170         | 200       | ms                    |                                                                                   |

|                                       |                           |                          | SMBus       | Timing    |                       |                                                                                   |

| Input Capacitance                     | C <sub>IN</sub>           |                          | 5           |           | pF                    |                                                                                   |

| Clock Frequency                       | f <sub>SMB</sub>          | 10                       |             | 400       | kHz                   |                                                                                   |

| Spike Suppression                     | t <sub>SP</sub>           |                          |             | 50        | ns                    |                                                                                   |

| Bus Free Time Stop<br>to Start        | t <sub>BUF</sub>          | 1.3                      |             |           | us                    |                                                                                   |

| Start Setup Time                      | t <sub>SU:STA</sub>       | 0.6                      |             |           | us                    |                                                                                   |

| Start Hold Time                       | t <sub>HD:STA</sub>       | 0.6                      |             |           | us                    |                                                                                   |

| Stop Setup Time                       | t <sub>SU:STO</sub>       | 0.6                      |             |           | us                    |                                                                                   |

| Data Hold Time                        | t <sub>HD:DAT</sub>       | 0                        |             |           | us                    | When transmitting to the master                                                   |

| Data Hold Time                        | t <sub>HD:DAT</sub>       | 0.3                      |             |           | us                    | When receiving from the master                                                    |

| Data Setup Time                       | t <sub>SU:DAT</sub>       | 0.6                      |             |           | us                    |                                                                                   |

| Clock Low Period                      | t <sub>LOW</sub>          | 1.3                      |             |           | us                    |                                                                                   |

| Clock High Period                     | t <sub>HIGH</sub>         | 0.6                      |             |           | us                    |                                                                                   |

| Clock / Data Fall<br>Time             | t <sub>FALL</sub>         |                          |             | 300       | ns                    | Min = 20+0.1C <sub>LOAD</sub> ns                                                  |

| Clock / Data Rise<br>Time             | t <sub>RISE</sub>         |                          |             | 300       | ns                    | Min = 20+0.1C <sub>LOAD</sub> ns                                                  |

| Capacitive Load                       | C <sub>LOAD</sub>         |                          |             | 400       | pF                    | per bus line                                                                      |

**Table 2.2 Electrical Specifications (continued)**

| $V_{DD} = 3V \text{ to}$         | $3.6V, T_A = 0$                          | °C to 85°C,          | all Typical | values at            | $T_A = 27^{\circ}C$ | unless otherwise noted.         |  |  |  |  |

|----------------------------------|------------------------------------------|----------------------|-------------|----------------------|---------------------|---------------------------------|--|--|--|--|

| CHARACTERISTIC                   | SYMBOL                                   | MIN                  | TYP         | MAX                  | UNIT                | CONDITIONS                      |  |  |  |  |

|                                  |                                          |                      | BC-Link     | Timing               |                     |                                 |  |  |  |  |

| Clock Period                     | t <sub>CLK</sub>                         | 250                  |             |                      | ns                  |                                 |  |  |  |  |

| Data Hold Time                   | t <sub>HD:DAT</sub>                      | 0                    |             |                      | ns                  |                                 |  |  |  |  |

| Data Setup Time                  | t <sub>SU:DAT</sub>                      | 30                   |             |                      | ns                  | Data must be valid before clock |  |  |  |  |

| Clock Duty Cycle                 | Duty                                     | 40                   | 50          | 60                   | %                   |                                 |  |  |  |  |

| SPI Timing                       |                                          |                      |             |                      |                     |                                 |  |  |  |  |

| Clock Period                     | t <sub>P</sub>                           | 250                  |             |                      | ns                  |                                 |  |  |  |  |

| Clock Low Period                 | t <sub>LOW</sub>                         | 0.4 x t <sub>P</sub> |             | 0.6 x t <sub>P</sub> | ns                  |                                 |  |  |  |  |

| Clock High Period                | t <sub>HIGH</sub>                        | 0.4 x t <sub>P</sub> |             | 0.6 x t <sub>P</sub> | ns                  |                                 |  |  |  |  |

| Clock Rise / Fall time           | t <sub>RISE</sub> /<br>t <sub>FALL</sub> |                      |             | 0.1 x t <sub>P</sub> | ns                  |                                 |  |  |  |  |

| Data Output Delay                | t <sub>D:CLK</sub>                       |                      |             | 10                   | ns                  |                                 |  |  |  |  |

| Data Setup Time                  | t <sub>SU:DAT</sub>                      | 20                   |             |                      | ns                  |                                 |  |  |  |  |

| Data Hold Time                   | t <sub>HD:DAT</sub>                      | 20                   |             |                      | ns                  |                                 |  |  |  |  |

| SPI_CS# to<br>SPI_CLK setup time | t <sub>SU:CS</sub>                       | 0                    |             |                      | ns                  |                                 |  |  |  |  |

| Wake Time                        | t <sub>WAKE</sub>                        | 10                   |             | 20                   | us                  | SPI_CS# asserted to CLK assert  |  |  |  |  |

Note 2.5 The ALERT pin will not glitch high or low at power up if connected to VDD or another voltage.

Note 2.6 The SMCLK and SMDATA pins will not glitch low at power up if connected to VDD or another voltage.

# **Chapter 3 Communications**

## 3.1 Communications

The CAP1126 communicates using the 2-wire SMBus or  $I^2C$  bus, the 2-wire proprietary BC-Link, or the SPI bus. Regardless of communication mechanism, the device functionality remains unchanged. The communications mechanism as well as the SMBus (or  $I^2C$ ) slave address is determined by the resistor connected between the ADDR\_COMM pin and ground as shown in Table 3.1.

**PULL-DOWN RESISTOR (+/- 5%)** PROTOCOL USED **SMBUS ADDRESS** SPI Communications using **GND** n/a Normal 4-wire Protocol Used SPI Communications using Bi-56k n/a Directional 3-wire Protocol Used 68k **BC-Link Communications** n/a SMBus / I<sup>2</sup>C 82k 0101\_100(r/w) SMBus / I<sup>2</sup>C 100k 0101\_011(r/w) SMBus / I<sup>2</sup>C 120k 0101\_010(r/w) 150k SMBus / I<sup>2</sup>C 0101\_001(r/w) **VDD** SMBus / I<sup>2</sup>C 0101\_000(r/w)

Table 3.1 ADDR\_COMM Pin Decode

# 3.1.1 SMBus (I<sup>2</sup>C) Communications

When configured to communicate via the SMBus, the CAP1126 supports the following protocols: Send Byte, Receive Byte, Read Byte, Write Byte, Read Block, and Write Block. In addition, the device supports  $I^2C$  formatting for block read and block write protocols.

**APPLICATION NOTE:** For SMBus/I<sup>2</sup>C communications, the SPI\_CS# pin is not used and should be grounded; any data presented to this pin will be ignored.

See Section 3.2 and Section 3.3 for more information on the SMBus bus and protocols respectively.

#### 3.1.2 SPI Communications

When configured to communicate via the SPI bus, the CAP1126 supports both bi-directional 3-wire and normal 4-wire protocols and uses the SPI\_CS# pin to enable communications.

See Section 3.5 and Section 3.6 for more information on the SPI bus and protocols respectively.

#### 3.1.3 BC-Link Communications

When BC-Link communications are used, the CAP1126 supports the read byte protocol and the write byte protocol.

**APPLICATION NOTE:** For BC-Link communications, the SPI\_CS# pin is not used and should be grounded; any data presented to this pin will be ignored.

See Section 3.8 for more information on the BC-Link Bus and protocols respectively.

**APPLICATION NOTE:** Upon power up, the CAP1126 will not respond to any communications for up to 15ms. After this time, full functionality is available.

## 3.2 System Management Bus

The CAP1126 communicates with a host controller, such as an SMSC SIO, through the SMBus. The SMBus is a two-wire serial communication protocol between a computer host and its peripheral devices. A detailed timing diagram is shown in Figure 3.1. Stretching of the SMCLK signal is supported; however, the CAP1126 will not stretch the clock signal.

Figure 3.1 SMBus Timing Diagram

## 3.2.1 SMBus Start Bit

The SMBus Start bit is defined as a transition of the SMBus Data line from a logic '1' state to a logic '0' state while the SMBus Clock line is in a logic '1' state.

## 3.2.2 SMBus Address and RD / WR Bit

The SMBus Address Byte consists of the 7-bit client address followed by the RD /  $\overline{WR}$  indicator bit. If this RD /  $\overline{WR}$  bit is a logic '0', then the SMBus Host is writing data to the client device. If this RD /  $\overline{WR}$  bit is a logic '1', then the SMBus Host is reading data from the client device.

See Table 3.1 for available SMBus addresses.

## 3.2.3 SMBus Data Bytes

All SMBus Data bytes are sent most significant bit first and composed of 8-bits of information.

#### 3.2.4 SMBus ACK and NACK Bits

The SMBus client will acknowledge all data bytes that it receives. This is done by the client device pulling the SMBus Data line low after the 8th bit of each byte that is transmitted. This applies to both the Write Byte and Block Write protocols.

The Host will NACK (not acknowledge) the last data byte to be received from the client by holding the SMBus data line high after the 8th data bit has been sent. For the Block Read protocol, the Host will ACK each data byte that it receives except the last data byte.

## 3.2.5 SMBus Stop Bit

The SMBus Stop bit is defined as a transition of the SMBus Data line from a logic '0' state to a logic '1' state while the SMBus clock line is in a logic '1' state. When the CAP1126 detects an SMBus Stop bit and it has been communicating with the SMBus protocol, it will reset its client interface and prepare to receive further communications.

#### 3.2.6 SMBus Timeout

The CAP1126 includes an SMBus timeout feature. Following a 30ms period of inactivity on the SMBus where the SMCLK pin is held low, the device will timeout and reset the SMBus interface.

The timeout function defaults to disabled. It can be enabled by setting the TIMEOUT bit in the Configuration register (see Section 5.6, "Configuration Registers").

## 3.2.7 SMBus and I<sup>2</sup>C Compatibility

The major differences between SMBus and I<sup>2</sup>C devices are highlighted here. For more information, refer to the SMBus 2.0 and I<sup>2</sup>C specifications. For information on using the CAP1126 in an I<sup>2</sup>C system, refer to SMSC AN 14.0 SMSC Dedicated Slave Devices in I<sup>2</sup>C Systems.

- 1. CAP1126 supports I<sup>2</sup>C fast mode at 400kHz. This covers the SMBus max time of 100kHz.

- 2. Minimum frequency for SMBus communications is 10kHz.

- 3. The SMBus client protocol will reset if the clock is held at a logic '0' for longer than 30ms. This timeout functionality is disabled by default in the CAP1126 and can be enabled by writing to the TIMEOUT bit. I<sup>2</sup>C does not have a timeout.

- 4. The SMBus client protocol will reset if both the clock and data lines are held at a logic '1' for longer than 200µs (idle condition). This function is disabled by default in the CAP1126 and can be enabled by writing to the TIMEOUT bit. I<sup>2</sup>C does not have an idle condition.

- 5. I<sup>2</sup>C devices do not support the Alert Response Address functionality (which is optional for SMBus).

- 6. I<sup>2</sup>C devices support block read and write differently. I<sup>2</sup>C protocol allows for unlimited number of bytes to be sent in either direction. The SMBus protocol requires that an additional data byte indicating number of bytes to read / write is transmitted. The CAP1126 supports I<sup>2</sup>C formatting only.

## 3.3 SMBus Protocols

The CAP1126 is SMBus 2.0 compatible and supports Write Byte, Read Byte, Send Byte, and Receive Byte as valid protocols as shown below.

All of the below protocols use the convention in Table 3.2.

Table 3.2 Protocol Format

| DATA SENT | DATA SENT TO |

|-----------|--------------|

| TO DEVICE | THE HOST     |

| Data sent | Data sent    |

## 3.3.1 SMBus Write Byte

The Write Byte is used to write one byte of data to a specific register as shown in Table 3.3.

**Table 3.3 Write Byte Protocol**

| START | SLAVE<br>ADDRESS | WR | ACK | REGISTER<br>ADDRESS | ACK | REGISTER<br>DATA | ACK | STOP   |

|-------|------------------|----|-----|---------------------|-----|------------------|-----|--------|

| 1 ->0 | YYYY_YYY         | 0  | 0   | XXh                 | 0   | XXh              | 0   | 0 -> 1 |

## 3.3.2 SMBus Read Byte

The Read Byte protocol is used to read one byte of data from the registers as shown in Table 3.4.

Table 3.4 Read Byte Protocol

| START | SLAVE<br>ADDRESS | WR | ACK | REGISTER<br>ADDRESS | ACK | START | CLIENT<br>ADDRESS | RD | ACK | REGISTER<br>DATA | NACK | STOP   |

|-------|------------------|----|-----|---------------------|-----|-------|-------------------|----|-----|------------------|------|--------|

| 1->0  | YYYY_YYY         | 0  | 0   | XXh                 | 0   | 1 ->0 | YYYY_YYY          | 1  | 0   | XXh              | 1    | 0 -> 1 |

## 3.3.3 SMBus Send Byte

The Send Byte protocol is used to set the internal address register pointer to the correct address location. No data is transferred during the Send Byte protocol as shown in Table 3.5.

APPLICATION NOTE: The Send Byte protocol is not functional in Deep Sleep (i.e., DSLEEP bit is set).

Table 3.5 Send Byte Protocol

| START  | SLAVE<br>ADDRESS | WR | ACK | REGISTER<br>ADDRESS | ACK | STOP   |

|--------|------------------|----|-----|---------------------|-----|--------|

| 1 -> 0 | YYYY_YYY         | 0  | 0   | XXh                 | 0   | 0 -> 1 |

## 3.3.4 SMBus Receive Byte

The Receive Byte protocol is used to read data from a register when the internal register address pointer is known to be at the right location (e.g., set via Send Byte). This is used for consecutive reads of the same register as shown in Table 3.6.

APPLICATION NOTE: The Receive Byte protocol is not functional in Deep Sleep (i.e., DSLEEP bit is set).

Table 3.6 Receive Byte Protocol

| START  | SLAVE<br>ADDRESS | RD | ACK | REGISTER DATA | NACK | STOP   |

|--------|------------------|----|-----|---------------|------|--------|

| 1 -> 0 | YYYY_YYY         | 1  | 0   | XXh           | 1    | 0 -> 1 |

# 3.4 I<sup>2</sup>C Protocols

The CAP1126 supports I<sup>2</sup>C Block Write and Block Read.

The protocols listed below use the convention in Table 3.2.

#### 3.4.1 Block Write

The Block Write is used to write multiple data bytes to a group of contiguous registers as shown in Table 3.7.

**APPLICATION NOTE:** When using the Block Write protocol, the internal address pointer will be automatically incremented after every data byte is received. It will wrap from FFh to 00h.

| START            | SLAVE<br>ADDRESS | WR               | ACK | REGISTER<br>ADDRESS | ACK              | REGISTER<br>DATA | ACK    |

|------------------|------------------|------------------|-----|---------------------|------------------|------------------|--------|

| 1 ->0            | YYYY_YYY         | 0                | 0   | XXh                 | 0                | XXh              | 0      |

| REGISTER<br>DATA | ACK              | REGISTER<br>DATA | ACK |                     | REGISTER<br>DATA | ACK              | STOP   |

| XXh              | 0                | XXh              | 0   |                     | XXh              | 0                | 0 -> 1 |

**Table 3.7 Block Write Protocol**

#### 3.4.2 Block Read

The Block Read is used to read multiple data bytes from a group of contiguous registers as shown in Table 3.8.

**APPLICATION NOTE:** When using the Block Read protocol, the internal address pointer will be automatically incremented after every data byte is received. It will wrap from FFh to 00h.

| START | SLAVE<br>ADDRESS | WR  | ACK              | REGISTER<br>ADDRESS | ACK              | START | SLAVE<br>ADDRESS | RD               | ACK  | REGISTER<br>DATA |

|-------|------------------|-----|------------------|---------------------|------------------|-------|------------------|------------------|------|------------------|

| 1->0  | YYYY_YYY         | 0   | 0                | XXh                 | 0                | 1 ->0 | YYYY_YYY         | 1                | 0    | XXh              |

| ACK   | REGISTER<br>DATA | ACK | REGISTER<br>DATA | ACK                 | REGISTER<br>DATA | ACK   |                  | REGISTER<br>DATA | NACK | STOP             |

| 0     | XXh              | 0   | XXh              | 0                   | XXh              | 0     |                  | XXh              | 1    | 0 -> 1           |

Table 3.8 Block Read Protocol

### 3.5 SPI Interface

The SMBus has a predefined packet structure, the SPI does not. The SPI Bus can operate in two modes of operation, normal 4-wire mode and bi-directional 3-wire mode. All SPI commands consist of 8-bit packets sent to a specific slave device (identified by the CS pin).

The SPI bus will latch data on the rising edge of the clock and the clock and data both idle high.

All commands are supported via both operating modes. The supported commands are: Reset Serial interface, set address pointer, write command and read command. Note that all other codes received during the command phase are ignored and have no effect on the operation of the device.

Figure 3.2 SPI Timing

#### 3.5.1 SPI Normal Mode

The SPI Bus can operate in two modes of operation, normal and bi-directional mode. In the normal mode of operation, there are dedicated input and output data lines. The host communicates by sending a command along the CAP1126 SPI\_MOSI data line and reading data on the SPI\_MISO data line. Both communications occur simultaneously which allows for larger throughput of data transactions.

All basic transfers consist of two 8 bit transactions from the Master device while the slave device is simultaneously sending data at the current address pointer value.

Data writes consist of two or more 8-bit transactions. The host sends a specific write command followed by the data to write the address pointer. Data reads consist of one or more 8-bit transactions. The host sends the specific read data command and continues clocking for as many data bytes as it wishes to receive.

#### 3.5.2 SPI Bi-Directional Mode

In the bi-directional mode of operation, the SPI data signals are combined into the SPI\_MSIO line, which is shared for data received by the device and transmitted by the device. The protocol uses a simple handshake and turn around sequence for data communications based on the number of clocks transmitted during each phase.

All basic transfers consist of two 8 bit transactions. The first is an 8 bit command phase driven by the Master device. The second is by an 8 bit data phase driven by the Master for writes, and by the CAP1126 for read operations.

The auto increment feature of the address pointer allows for successive reads or writes. The address pointer will return to 00h after reaching FFh.

### 3.5.3 SPI CS# Pin

The SPI Bus is a single master, multiple slave serial bus. Each slave has a dedicated CS pin (chip select) that the master asserts low to identify that the slave is being addressed. There are no formal addressing options.

### 3.5.4 Address Pointer

All data writes and reads are accessed from the current address pointer. In both Bi-directional mode and Full Duplex mode, the Address pointer is automatically incremented following every read command or every write command.

The address pointer will return to 00h after reaching FFh.

## 3.5.5 SPI Timeout

The CAP1126 does not detect any timeout conditions on the SPI bus.

### 3.6 Normal SPI Protocols

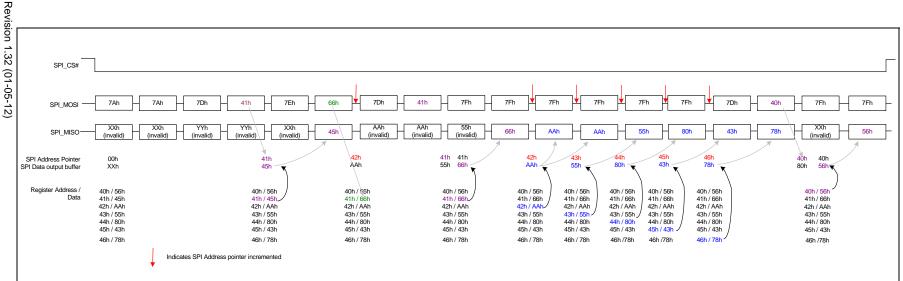

When operating in normal mode, the SPI bus internal address pointer is incremented depending upon which command has been transmitted. Multiple commands may be transmitted sequentually so long as the SPI\_CS# pin is asserted low. Figure 3.3 shows an example of this operation.

Figure 3.3 Example SPI Bus Communication - Normal Mode

## 3.6.1 Reset Interface

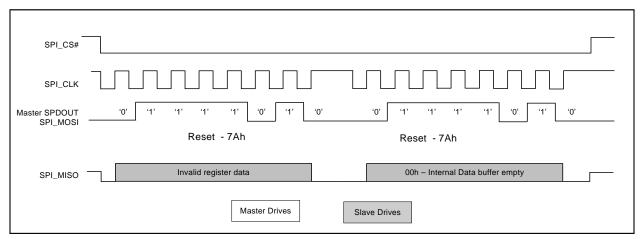

Resets the Serial interface whenever two successive 7Ah codes are received. Regardless of the current phase of the transaction - command or data, the receipt of the successive reset commands resets the Serial communication interface only. All other functions are not affected by the reset operation.

Figure 3.4 SPI Reset Interface Command - Normal Mode

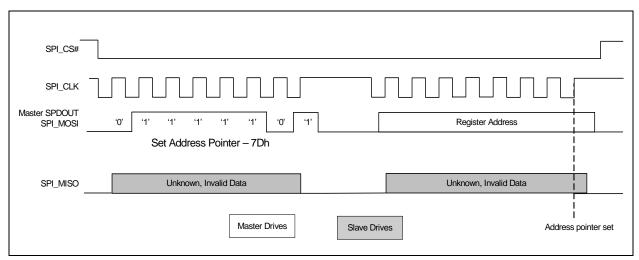

#### 3.6.2 Set Address Pointer

The Set Address Pointer command sets the Address pointer for subsequent reads and writes of data. The pointer is set on the rising edge of the final data bit. At the same time, the data that is to be read is fetched and loaded into the internal output buffer but is not transmitted.

Figure 3.5 SPI Set Address Pointer Command - Normal Mode

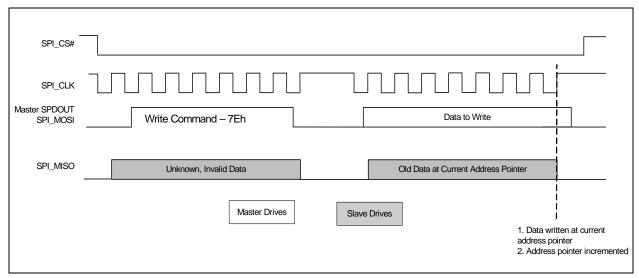

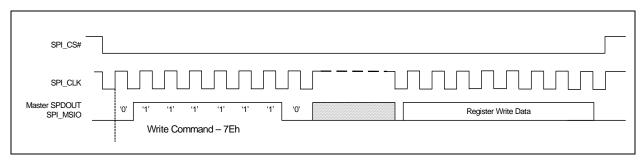

### 3.6.3 Write Data

The Write Data protocol updates the contents of the register referenced by the address pointer. As the command is processed, the data to be read is fetched and loaded into the internal output buffer but not transmitted. Then, the register is updated with the data to be written. Finally, the address pointer is incremented.

Figure 3.6 SPI Write Command - Normal Mode

#### 3.6.4 Read Data

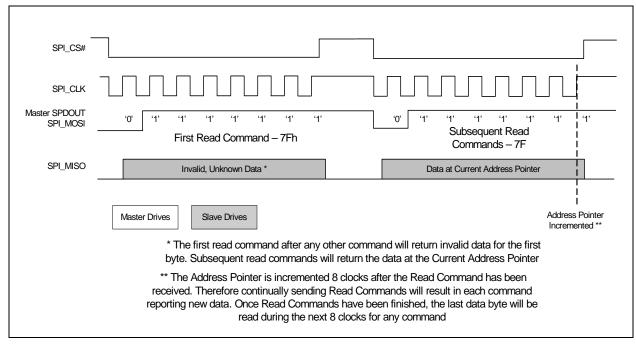

The Read Data protocol is used to read data from the device. During the normal mode of operation, while the device is receiving data, the CAP1126 is simultaneously transmitting data to the host. For the Set Address commands and the Write Data commands, this data may be invalid and it is recommended that the Read Data command is used.

Figure 3.7 SPI Read Command - Normal Mode

Figure 3.8 SPI Read Command - Normal Mode - Full

## 3.7 Bi-Directional SPI Protocols

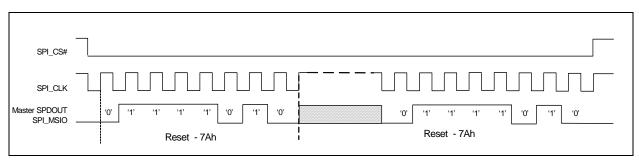

### 3.7.1 Reset Interface

Resets the Serial interface whenever two successive 7Ah codes are received. Regardless of the current phase of the transaction - command or data, the receipt of the successive reset commands resets the Serial communication interface only. All other functions are not affected by the reset operation.

Figure 3.9 SPI Reset Interface Command - Bi-directional Mode

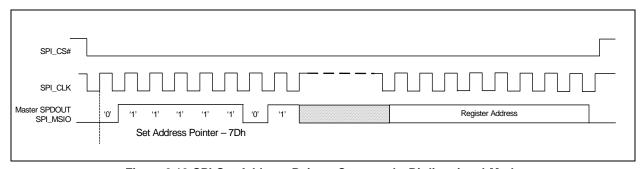

#### 3.7.2 Set Address Pointer

Sets the address pointer to the register to be accessed by a read or write command. This command overrides the auto-incrementing of the address pointer.

Figure 3.10 SPI Set Address Pointer Command - Bi-directional Mode

### 3.7.3 Write Data

Writes data value to the register address stored in the address pointer. Performs auto increment of address pointer after the data is loaded into the register.

Figure 3.11 SPI Write Data Command - Bi-directional Mode

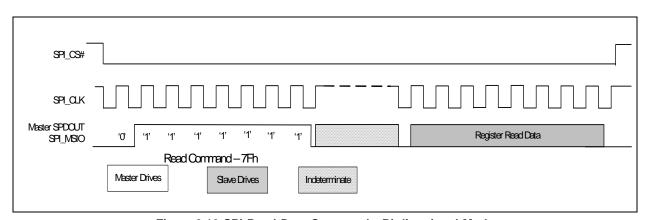

#### 3.7.4 Read Data

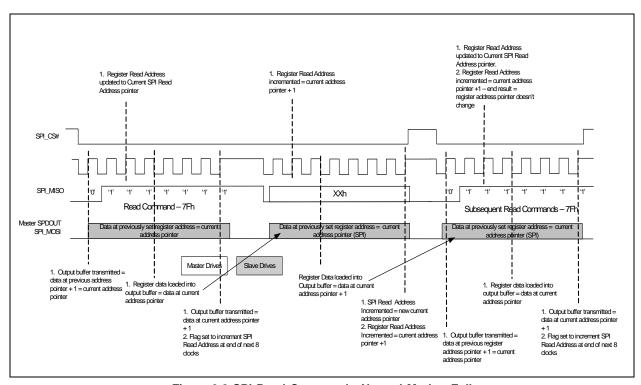

Reads data referenced by the address pointer. Performs auto increment of address pointer after the data is transferred to the Master.

Figure 3.12 SPI Read Data Command - Bi-directional Mode

## 3.8 BC-Link Interface

The BC-Link is a proprietary bus developed to allow communication between a host controller device to a companion device. This device uses this serial bus to read and write registers and for interrupt processing. The interface uses a data port concept, where the base interface has an address register, data register and a control register, defined in the SMSC's 8051's SFR space.

Refer to documentation for the BC-Link compatible host controller for details on how to access the CAP1126 via the BC-Link Interface.

# **Chapter 4 General Description**

The CAP1126 is a multiple channel Capacitive Touch sensor with multiple power LED drivers. It contains six (6) individual capacitive touch sensor inputs with programmable sensitivity for use in touch sensor applications. Each sensor input automatically recalibrates to compensate for gradual environmental changes.

The CAP1126 also contains two (2) low side (or push-pull) LED drivers that offer full-on / off, variable rate blinking, dimness controls, and breathing. Each of the LED drivers may be linked to one of the sensor inputs to be actuated when a touch is detected. As well, each LED driver may be individually controlled via a host controller.

Finally, the device contains a dedicated RESET pin to act as a soft reset by the system.

The CAP1126 offers multiple power states. It operates at the lowest quiescent current during its Deep Sleep state. In the low power Standby state, it can monitor one or more channels and respond to communications normally. The device contains a wake pin (WAKE/SPI\_MOSI) output to wake the system when a touch is detected in Standby and to wake the device from Deep Sleep.

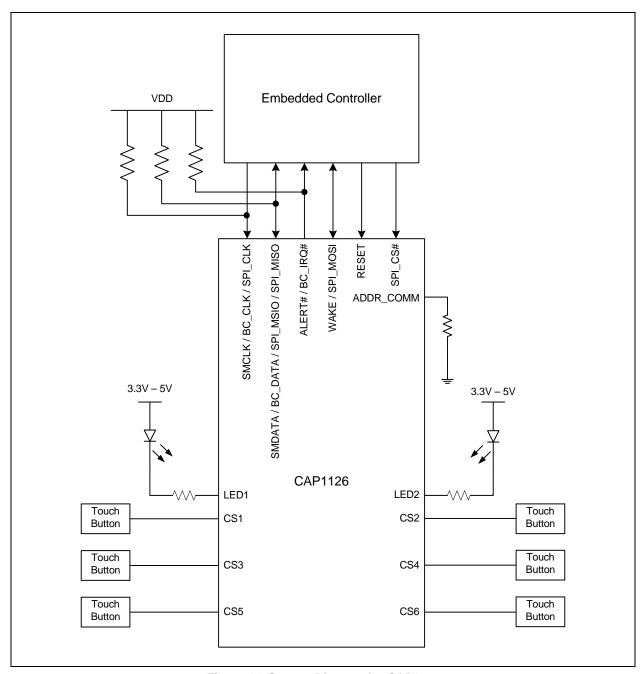

The device communicates with a host controller using the SPI bus, SMSC BC-Link bus, or via SMBus /  $I^2C$ . The host controller may poll the device for updated information at any time or it may configure the device to flag an interrupt whenever a touch is detected on any sensor pad.

A typical system diagram is shown in Figure 4.1.

Figure 4.1 System Diagram for CAP1126

## 4.1 Power States

The CAP1126 has three operating states depending on the status of the STBY and DSLEEP bits. When the device transitions between power states, previously detected touches (for inactive channels) are cleared and the status bits reset.

- 1. Fully Active The device is fully active. It is monitoring all active capacitive sensor inputs and driving all LED channels as defined.

- 2. Standby The device is in a lower power state. It will measure a programmable number of channels using the Standby Configuration controls (see Section 5.20 through Section 5.22). Interrupts will still be generated based on the active channels. The device will still respond to communications normally and can be returned to the Fully Active state of operation by clearing the STBY bit.

- 3. Deep Sleep The device is in its lowest power state. It is not monitoring any capacitive sensor inputs and not driving any LEDs. All LEDs will be driven to their programmed non-actuated state and no PWM operations will be done. While in Deep Sleep, the device can be awakened by SMBus or SPI communications targeting the device. This will not cause the DSLEEP to be cleared so the device will return to Deep Sleep once all communications have stopped.

If the device is not communicating via the 4-wire SPI bus, then during this state of operation, if the WAKE/SPI\_MOSI pin is driven high by an external source, the device will clear the DSLEEP bit and return to Fully Active.

**APPLICATION NOTE:** In the Deep Sleep state, the LED output will be either high or low and will not be PWM'd at the min or max duty cycle.

**APPLICATION NOTE:** If the CAP1126 is configured to communicate using the BC-Link protocol, the device does not support Deep Sleep.

#### 4.2 RESET Pin

The RESET pin is an active high reset that is driven from an external source. While it is asserted high, all the internal blocks will be held in reset including the communications protocol used. No capacitive touch sensor inputs will be sampled and the LEDs will not be driven. All configuration settings will be reset to default states and all readings will be cleared.

The device will be held in Deep Sleep that can only be removed by driving the RESET pin low. This will cause the RESET status bit to be set to a logic '1' and generate an interrupt.

## 4.3 WAKE/SPI\_MOSI Pin Operation

The WAKE / SPI\_MOSI pin is a multi-function pin depending on device operation. When the device is configured to communicate using the 4-wire SPI bus, this pin is an input.

However, when the CAP1126 is placed in Standby and is not communicating using the 4-wire SPI protocol, the WAKE pin is an active high output. In this condition, the device will assert the WAKE/SPI\_MOSI pin when a touch is detected on one of its sampled sensor inputs. The pin will remain asserted until the INT bit has been cleared and then it will be de-asserted.

When the CAP1126 is placed in Deep Sleep and it is not communicating using the 4-wire SPI protocol, the WAKE/SPI\_MOSI pin is monitored by the device as an input. If the WAKE/SPI\_MOSI pin is driven high by an external source, the CAP1126 will clear the DSLEEP bit causing the device to return to Fully Active.

When the device is placed in Deep Sleep, this pin is a High-Z input and must have a pull-down resistor to GND for proper operation.

#### 4.4 LED Drivers

The CAP1126 contains two (2) LED drivers. Each LED driver can be linked to its respective capacitive touch sensor input or it can be controlled by the host. Each LED driver can be configured to operate in one of the following modes with either push-pull or open drain drive.

- Direct The LED is configured to be on or off when the corresponding input stimulus is on or off (or inverted). The brightness of the LED can be programmed from full off to full on (default). Additionally, the LED contains controls to individually configure ramping on, off, and turn-off delay.

- 2. Pulse 1 The LED is configured to "Pulse" (transition ON-OFF-ON) a programmable number of times with programmable rate and min / max brightness. This behavior may be actuated when a press is detected or when a release is detected.

- 3. Pulse 2 The LED is configured to "Pulse" while actuated and then "Pulse" a programmable number of times with programmable rate and min / max brightness when the sensor pad is released.

- 4. Breathe The LED is configured to transition continuously ON-OFF-ON (i.e. to "Breathe") with a programmable rate and min / max brightness.

When an LED is not linked to a sensor and is actuated by the host, there's an option to assert the ALERT# pin when the initiated LED behavior has completed.

## 4.4.1 Linking LEDs to Capacitive Touch Sensor Inputs

All LEDs can be linked to the corresponding capacitive touch sensor input so that when the sensor input detects a touch, the corresponding LED will be actuated at one of the programmed responses.

## 4.5 Capacitive Touch Sensing

The CAP1126 contains six (6) independent capacitive touch sensor inputs. Each sensor input has dynamic range to detect a change of capacitance due to a touch. Additionally, each sensor input can be configured to be automatically and routinely re-calibrated.

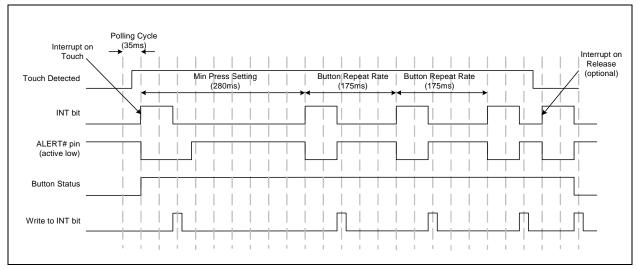

## 4.5.1 Sensing Cycle