## MAC8SDG, MAC8SMG, MAC8SNG

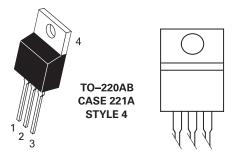

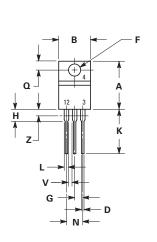

#### **Pin Out**

## **Description**

Designed primarily for full-wave ac control applications, such as motor controls, heating controls and power supplies; or wherever half-wave silicon gate-controlled, solid-state devices are needed.

#### **Features**

- Sensitive Gate Allows Triggering by Microcontrollers and other Logic Circuits

- Uniform Gate Trigger Currents in Three Quadrants; Q1,

Q2, and Q3

- High Immunity to dv/dt 25 V/µs Minimum at 110°C

- High Commutating di/dt 8.0 A/ms Minimum at 110°C

- Maximum Values of IGT, VGT and IH Specified for Ease of Design

- On-State Current Rating of 8 Amperes RMS at 70°C

- High Surge Current Capability 70 Amperes

- Blocking Voltage to 800 Volts

- Rugged, Economical TO-220 Package

- These Devices are Pb-Free and are RoHS Compliant

#### **Functional Diagram**

## Additional Information

Samples

# **Thyristors**

## **Maximum Ratings** $(T_J = 25^{\circ}C \text{ unless otherwise noted})$

| Rating                                                                                                                                | Symbol               | Value             | Unit               |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|--------------------|

| Peak Repetitive Off-State Voltage (Note 1)  (Gate Open, Sine Wave 50 to 60 Hz, T <sub>J</sub> = 25° to 100°C)  MAC8SD  MAC8SM  MAC8SN | G V RRM              | 400<br>600<br>800 | V                  |

| On-State RMS Current (Full Cycle Sine Wave, 60 Hz, T <sub>C</sub> = 100°C)                                                            | I <sub>T (RMS)</sub> | 8.0               | А                  |

| Peak Non-Repetitive Surge Current<br>(One Full Cycle Sine Wave, 60 Hz, T <sub>J</sub> = 125°C)                                        | I <sub>TSM</sub>     | 70                | А                  |

| Circuit Fusing Consideration (t = 8.3 ms)                                                                                             | l <sup>2</sup> t     | 20                | A <sup>2</sup> sec |

| Peak Gate Power (Pulse Width $\leq 1.0 \mu s$ , $T_{c} = 80^{\circ}C$ )                                                               | P <sub>GM</sub>      | 16                | W                  |

| Average Gate Power (t = $8.3 \text{ ms}$ , $T_c = 80^{\circ}\text{C}$ )                                                               | P <sub>G (AV)</sub>  | 0.35              | W                  |

| Operating Junction Temperature Range                                                                                                  | T <sub>J</sub>       | -40 to +110       | °C                 |

| Storage Temperature Range                                                                                                             | T <sub>stg</sub>     | -40 to +150       | °C                 |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## **Thermal Characteristics**

| Rating                                                                         |                                           | Symbol           | Value       | Unit |

|--------------------------------------------------------------------------------|-------------------------------------------|------------------|-------------|------|

| Thermal Resistance,                                                            | Junction-to-Case (AC) Junction-to-Ambient | R <sub>8JC</sub> | 2.2<br>62.5 | °C/W |

| Maximum Lead Temperature for Soldering Purposes, 1/8" from case for 10 seconds |                                           | $T_{L}$          | 260         | °C   |

<sup>1.</sup> V<sub>DRM</sub> and V<sub>RRM</sub> for all types can be applied on a continuous basis. Ratings apply for zero or negative gate voltage; however, positive gate voltage shall not be applied concurrent with negative potential on the anode. Blocking voltages shall not be tested with a constant current source such that the voltage ratings of the devices are exceeded.

# **Thyristors**

## **Electrical Characteristics** - **OFF** $(T_j = 25^{\circ}\text{C unless otherwise noted})$ ; Electricals apply in both directions)

| Characteristic                         |                        | Symbol             | Min | Тур | Max  | Unit  |

|----------------------------------------|------------------------|--------------------|-----|-----|------|-------|

| Peak Repetitive Blocking Current       | $T_{J} = 25^{\circ}C$  | l <sub>DRM</sub> , | -   | -   | 0.01 |       |

| $(V_D = V_{DRM} = V_{RRM}, Gate Open)$ | T <sub>J</sub> = 110°C | I <sub>RRM</sub>   | -   | -   | 2.0  | mA mA |

## **Electrical Characteristics** - **ON** $(T_J = 25^{\circ}\text{C unless otherwise noted; Electricals apply in both directions)$

| Characteristic                                                                                   |              | Symbol          | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------------------------|--------------|-----------------|------|------|------|------|

| Peak On-State Voltage (Note 4) (I <sub>TM</sub> = ±11 A)                                         |              | V <sub>TM</sub> | _    | _    | 1.85 | V    |

|                                                                                                  | MT2(+), G(+) |                 | -    | 2.0  | 5.0  | mA   |

| Gate Trigger Current (Continuous dc)                                                             | MT2(+), G(-) | I <sub>GT</sub> | -    | 3.0  | 5.0  |      |

| $(V_{D} = 12 \text{ V}, \text{ R}_{L} = 100 \Omega)$                                             | MT2(-), G(-) | -               | _    | 3.0  | 5.0  |      |

| Holding Current ( $V_D = 12 \text{ V}$ , Gate Open, Initiating Current = $\pm 150 \text{ mA}$ )) |              | I <sub>H</sub>  | -    | 3.0  | 10   | mA   |

|                                                                                                  | MT2(+), G(+) | I <sub>L</sub>  | -    | 5.0  | 15   | mA   |

| Latching Current $(V_D = 24 \text{ V}, I_G = 5 \text{ mA})$                                      | MT2(+), G(-) |                 | _    | 10   | 20   |      |

|                                                                                                  | MT2(-), G(-) |                 | _    | 5.0  | 15   |      |

|                                                                                                  | MT2(+), G(+) |                 | 0.45 | 0.62 | 1.5  |      |

| Gate Trigger Voltage ( $V_D = 12 \text{ V}, R_L = 100 \Omega$ )                                  | MT2(+), G(-) | V <sub>GT</sub> | 0.45 | 0.60 | 1.5  | V    |

|                                                                                                  | MT2(-), G(-) |                 | 0.45 | 0.65 | 1.5  |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Indicates Pulse Test: Pulse Width  $\leq$  2.0 ms, Duty Cycle  $\leq$  2%.

## **Dynamic Characteristics**

| Characteristic                                                                                                                                                                                                               |  | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|-----|-----|------|

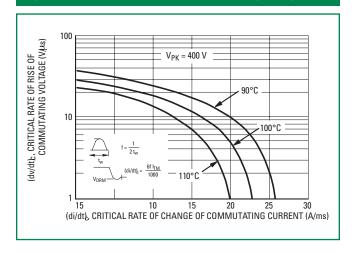

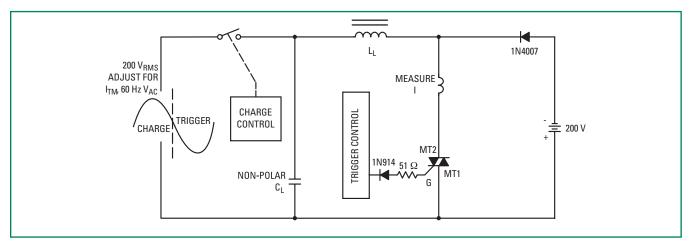

| Rate of Change of Commutating Current See Figure 10. ( $V_D = 400 \text{ V}, I_{TM} = 4.4 \text{ A}$ , Commutating dv/dt = 18 V/µs,Gate Open, TJ = 125°C, f = 250 Hz, No Snubber) $C_L = 10 \text{ µF } L_L = 40 \text{ mH}$ |  | 8.0 | 10  | _   | A/ms |

| Critical Rate of Rise of Off-State Voltage ( $V_D$ = Rated $V_{DRM}$ , Exponential Waveform, $R_{GK}$ = 510 $\Omega$ , $T_J$ = 110°C)                                                                                        |  | 25  | 75  | _   | V/µs |

## Surface Mount - 50V > MAC8SDG, MAC8SMG, MAC8SNG

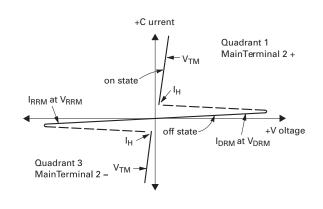

## **Voltage Current Characteristic of SCR**

| Symbol           | Parameter                                 |  |

|------------------|-------------------------------------------|--|

| $V_{DRM}$        | Peak Repetitive Forward Off State Voltage |  |

| I <sub>DRM</sub> | Peak Forward Blocking Current             |  |

| V <sub>RRM</sub> | Peak Repetitive Reverse Off State Voltage |  |

| I <sub>RRM</sub> | Peak Reverse Blocking Current             |  |

| V <sub>TM</sub>  | Maximum On State Voltage                  |  |

| I <sub>H</sub>   | Holding Current                           |  |

**Thyristors**

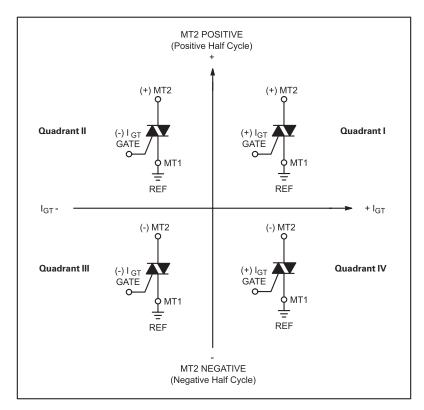

## **Quadrant Definitions for a Triac**

All polarities are referenced to MT1.

With in-phase signals (using standard AC lines) quadrants I and III are used.

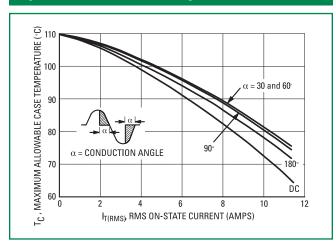

**Figure 1. RMS Current Derating**

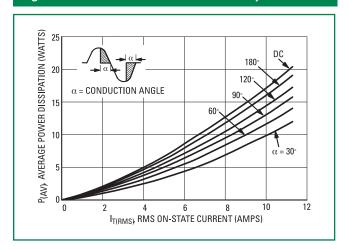

Figure 2. Maximum On-State Power Dissipation

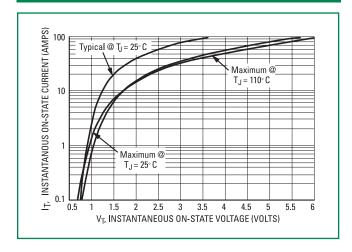

Figure 3. On-State Characteristics

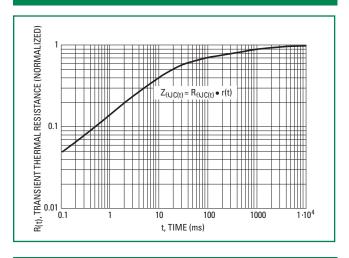

**Figure 4. Transient Thermal Response**

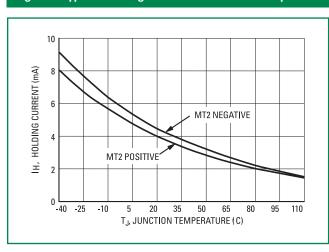

Figure 5. Typical Holding Current Vs. Junction Temperature

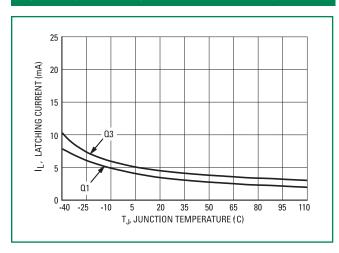

Figure 6. Typical Latching Current Vs. Junction Temperature

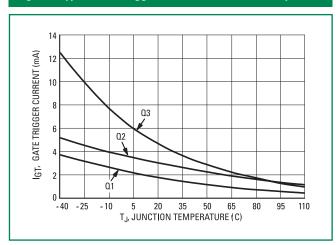

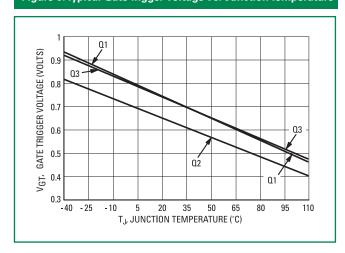

#### Figure 7. Typical Gate Trigger Current Vs. Junction Temperature

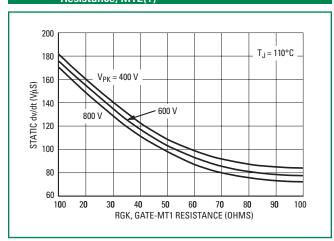

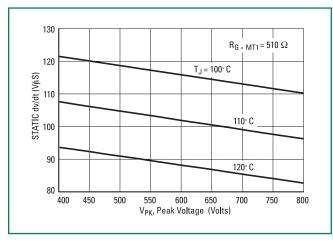

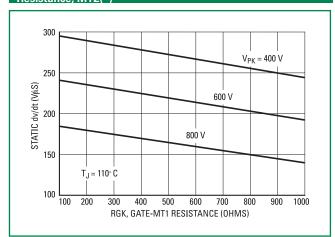

Figure 9. Typical Exponential Static dv/dt Vs. Gate-MT1 Resistance, MT2(+)

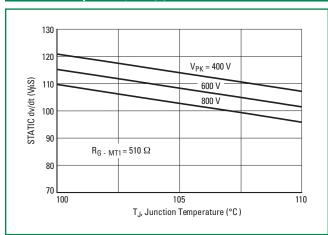

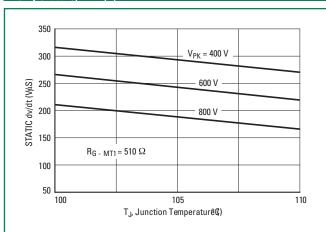

Figure 11. Typical Exponential Static dv/dt Vs. Junction Temperature, MT2(+)

Figure 8. Typical Gate Trigger Voltage Vs. Junction Temperature

Figure 10.Typical Exponential Static dv/dt Versus Peak Voltage, MT2(+)

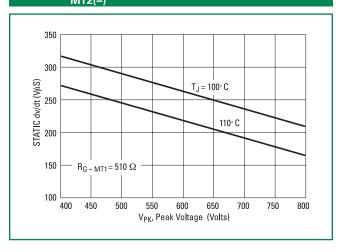

Figure 12. Typical Exponential Static dv/dt Vs. Peak Voltage,

Figure 13. Typical Exponential Static dv/dt Versus Junction Temperature, MT2(–)

Figure 14. Typical Exponential Static dv/dt Versus Gate-MT1 Resistance, MT2(-)

Figure 15. Critical Rate of Rise of Commutating Voltage

Figure 16. Simplified Test Circuit to Measure the Critical Rate of Rise of Commutating Current (di/dt)

Note: Component values are for verification of rated (di/dt)<sub>c</sub>. See AN1048 for additional information.

## Surface Mount - 50V > MAC8SDG, MAC8SMG, MAC8SNG

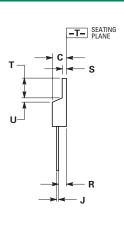

#### **Dimensions**

| <b>S</b> : | Inches |       | Millim | neters |

|------------|--------|-------|--------|--------|

| Dim        | Min    | Max   | Min    | Max    |

| А          | 0.570  | 0.620 | 14.48  | 15.75  |

| В          | 0.380  | 0.405 | 9.66   | 10.28  |

| С          | 0.160  | 0.190 | 4.07   | 4.82   |

| D          | 0.025  | 0.035 | 0.64   | 0.88   |

| F          | 0.142  | 0.147 | 3.61   | 3.73   |

| G          | 0.095  | 0.105 | 2.42   | 2.66   |

| Н          | 0.110  | 0.155 | 2.80   | 3.93   |

| J          | 0.014  | 0.022 | 0.36   | 0.55   |

| K          | 0.500  | 0.562 | 12.70  | 14.27  |

| L          | 0.045  | 0.060 | 1.15   | 1.52   |

| N          | 0.190  | 0.210 | 4.83   | 5.33   |

| Q          | 0.100  | 0.120 | 2.54   | 3.04   |

| R          | 0.080  | 0.110 | 2.04   | 2.79   |

| S          | 0.045  | 0.055 | 1.15   | 1.39   |

| Т          | 0.235  | 0.255 | 5.97   | 6.47   |

| U          | 0.000  | 0.050 | 0.00   | 1.27   |

| V          | 0.045  |       | 1.15   |        |

| Z          |        | 0.080 |        | 2.04   |

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION Z DEFINES A ZONE WHERE ALL BODY AND LEAD IRREGULARITIES ARE ALLOWED.

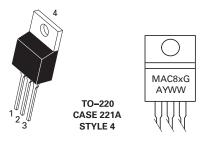

## **Part Marking System**

= D, M, or N

A= Assembly Location (Optional)\*

/= Year

WW = Work Week

G = Pb-Free Package

\* The Assembly Location code (A) is optional. In cases where the Assembly Location is stamped on the package the assembly code may be blank.

| Pin Assignment |                 |

|----------------|-----------------|

| 1              | Main Terminal 1 |

| 2              | Main Terminal 2 |

| 3              | Gate            |

| 4              | Main Terminal 2 |

## **Ordering Information**

| Device  | Package               | Shipping        |

|---------|-----------------------|-----------------|

| MAC8SDG |                       |                 |

| MAC8SMG | TO-220AB<br>(Pb-Free) | 50 Units / Rail |

| MAC8SNG |                       |                 |

**Disclaimer Notice** - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littlefuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at: <a href="https://www.littlefuse.com/disclaimer-electronics">www.littlefuse.com/disclaimer-electronics</a>